NEC Network Controller uPD98502 User Manual

Page 81

CHAPTER 2 V

R

4120A

Preliminary User’s Manual S15543EJ1V0UM

81

2.2.2.4 Special instructions

Special instructions generate software exceptions. Their formats are R-type (Syscall, Break). The Trap instruction

is available only for the V

R

4000 Series. All the other instructions are available for all V

R

Series.

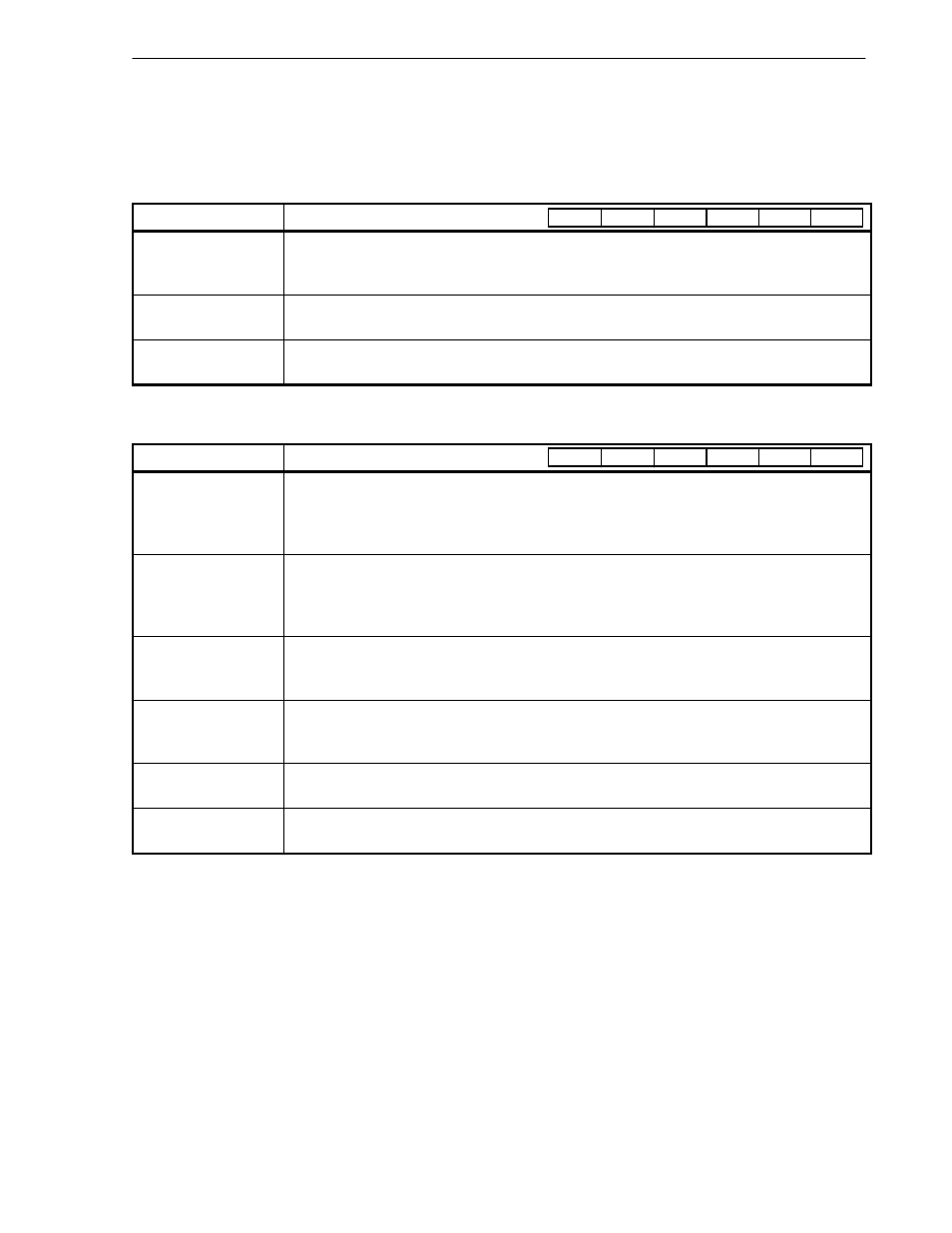

Table 2-19. Special Instructions

Instruction

Format and Description

Synchronize

SYNC

Completes the load/store instruction executing in the current pipeline before the next load/store

instruction starts execution.

System Call

SYSCALL

Generates a system call exception, and then transits control to the exception handling program.

Breakpoint

BREAK

Generates a break point exception, and then transits control to the exception handling program.

Table 2-20. Special Instructions (Extended ISA) (1/2)

Instruction

Format and Description

Trap If Greater Than Or

Equal

TGE rs, rt

The contents of register rs are compared with that of register rt, treating both operands as signed

integers. If the contents of register rs are greater than or equal to that of register rt, an exception

occurs.

Trap If Greater Than Or

Equal Unsigned

TGEU rs, rt

The contents of register rs are compared with that of register rt, treating both operands as unsigned

integers. If the contents of register rs are greater than or equal to that of register rt, an exception

occurs.

Trap If Less Than

TLT rs, rt

The contents of register rs are compared with that of register rt, treating both operands as signed

integers. If the contents of register rs are less than that of register rt, an exception occurs.

Trap If Less Than

Unsigned

TLTU rs, rt

The contents of register rs are compared with that of register rt, treating both operands as unsigned

integers. If the contents of register rs are less than that of register rt, an exception occurs.

Trap If Equal

TEQ rs, rt

If the contents of registers rs and rt are equal, an exception occurs.

Trap If Not Equal

TNE rs, rt

If the contents of registers rs and rt are not equal, an exception occurs.

SPECIAL

rs

rt

funct

rd

sa

SPECIAL

rs

rt

funct

rd

sa