A.3 jump and branch instructions – NEC Network Controller uPD98502 User Manual

Page 434

APPENDIX A MIPS III INSTRUCTION SET DETAILS

434

Preliminary User’s Manual S15543EJ1V0UM

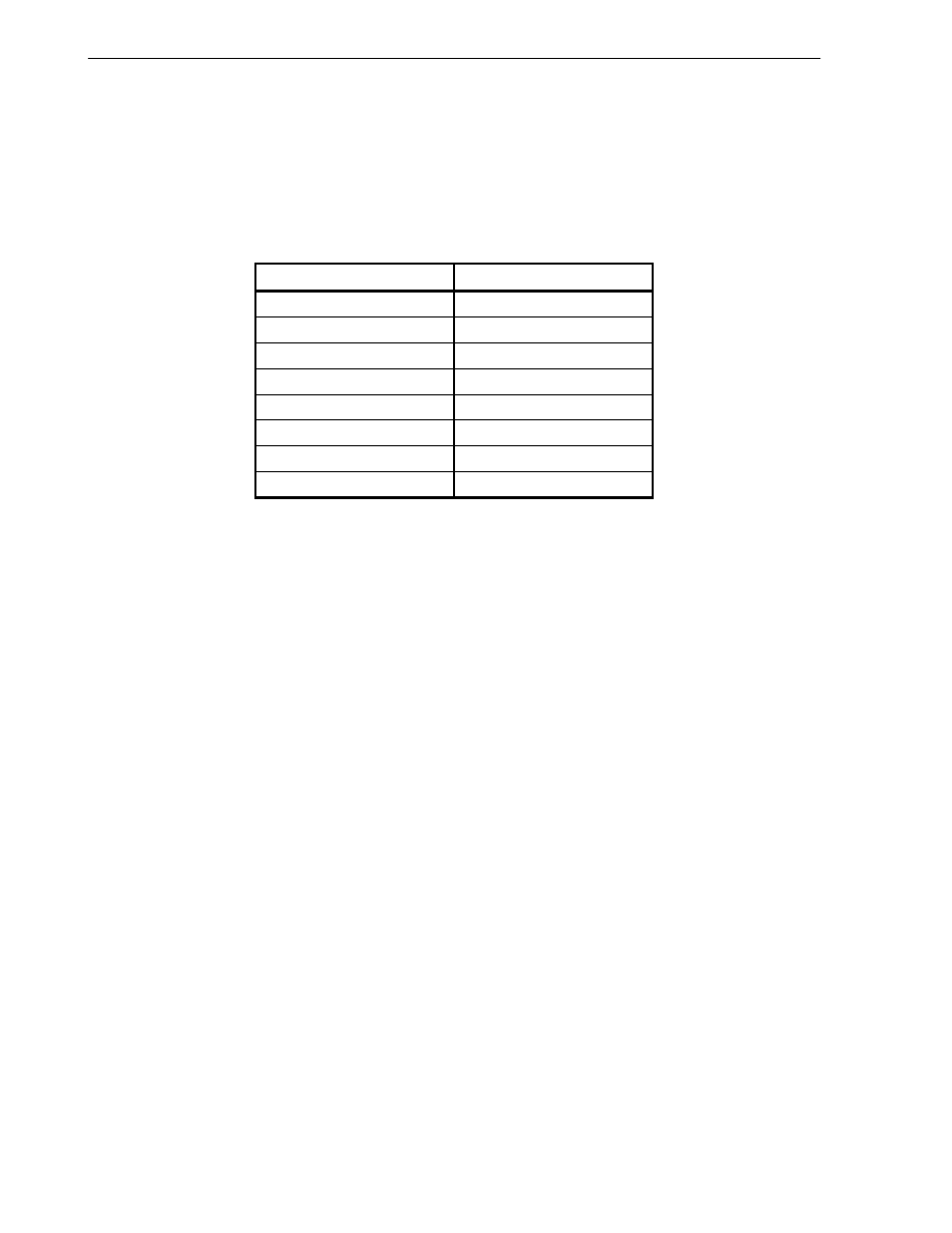

As shown in Table A-3, the Access Type field indicates the size of the data item to be loaded or stored.

Regardless of access type or byte-numbering order (endian), the address specifies the byte that has the smallest byte

address in the addressed field. This is the rightmost byte in the V

R

4120A CPU since it supports the little-endian order

only.

Table A-3. Access Type Specifications for Loads/Stores

Access Type

Description

DOUBLEWORD

8 bytes (64 bits)

SEPTIBYTE

7 bytes (56 bits)

SEXTIBYTE

6 bytes (48 bits)

QUINTIBYTE

5 bytes (40 bits)

WORD

4 bytes (32 bits)

TRIPLEBYTE

3 bytes (24 bits)

HALFWORD

2 bytes (16 bits)

BYTE

1 byte (8 bits)

The bytes within the addressed doubleword that are used can be determined directly from the access type and the

three low-order bits of the address.

A.3 Jump and Branch Instructions

All jump and branch instructions have an architectural delay of exactly one instruction. That is, the instruction

immediately following a jump or branch (that is, occupying the delay slot) is always executed while the target

instruction is being fetched from storage. A delay slot may not itself be occupied by a jump or branch instruction;

however, this error is not detected and the results of such an operation are undefined.

If an exception or interrupt prevents the completion of a legal instruction during a delay slot, the hardware sets the

EPC register to point at the jump or branch instruction that precedes it. When the code is restarted, both the jump or

branch instructions and the instruction in the delay slot are reexecuted.

Because jump and branch instructions may be restarted after exceptions or interrupts, they must be restartable.

Therefore, when a jump or branch instruction stores a return link value, register

r31 (the register in which the link is

stored) may not be used as a source register.

Since instructions must be word-aligned, a Jump Register

or Jump and Link Register instruction must use a

register which contains an address whose two low-order bits (low-order one bit in the 16-bit mode) are zero. If these

low-order bits are not zero, an address exception will occur when the jump target instruction is subsequently fetched.