NEC Network Controller uPD98502 User Manual

Page 78

CHAPTER 2 V

R

4120A

78

Preliminary User’s Manual S15543EJ1V0UM

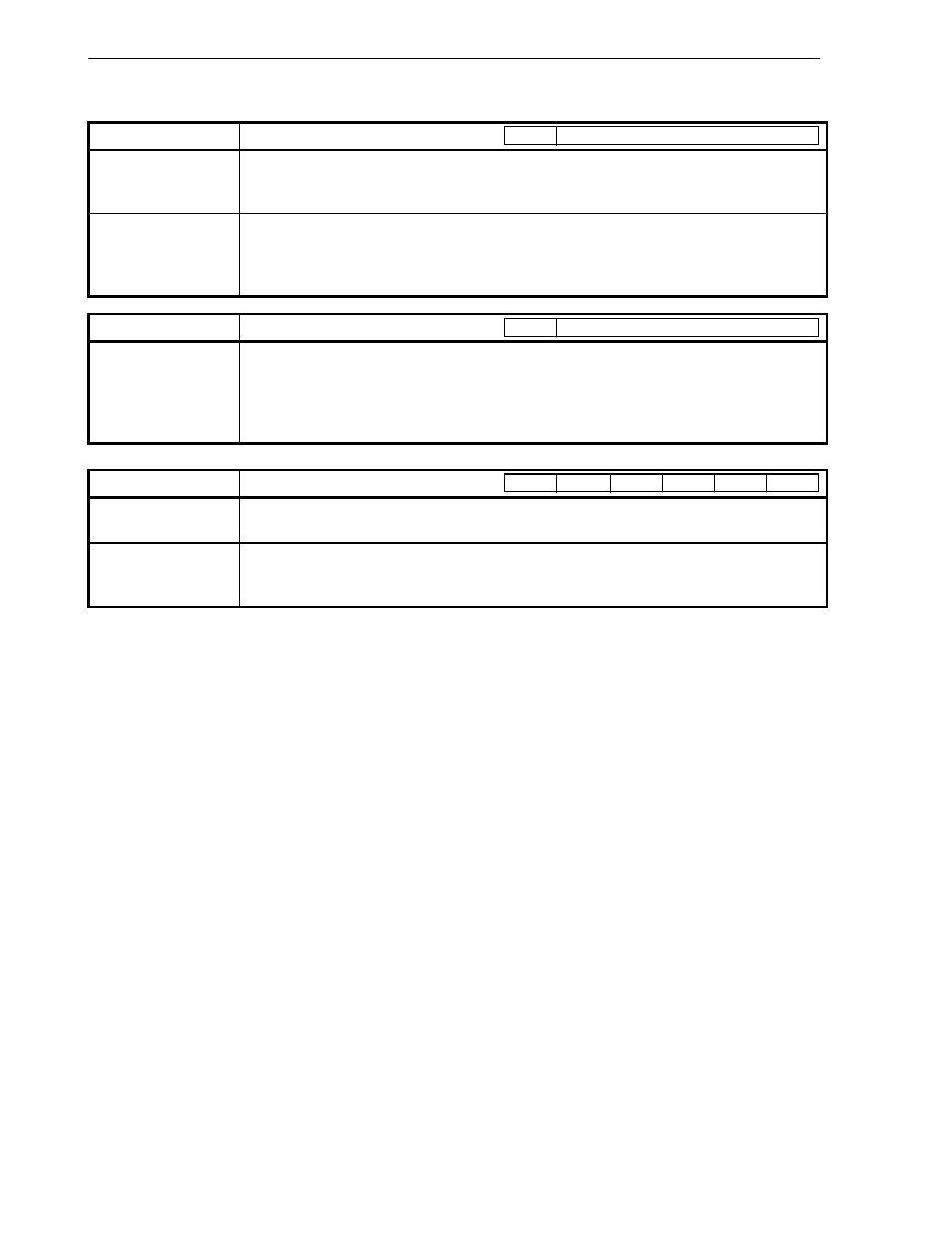

Table 2-16. Jump Instruction

Instruction

Format and Description

Jump

JAL target

The contents of 26-bit target address is shifted left by two bits and combined with the high-order four

bits of the PC. The program jumps to this calculated address with a delay of one instruction.

Jump And Link

J target

The contents of 26-bit target address is shifted left by two bits and combined with the high-order four

bits of the PC. The program jumps to this calculated address with a delay of one instruction. The

address of the instruction following the delay slot is stored into r31 (link register).

Instruction

Format and Description

Jump And Link

Exchange

JALX target

The contents of 26-bit target address is shifted left by two bits and combined with the high-order four

bits of the PC. The program jumps to this calculated address with a delay of one instruction, and then

the ISA mode bit is reversed. The address of the instruction following the delay slot is stored into r31

(link register).

Instruction

Format and Description

Jump Register

JR rs

The program jumps to the address specified in register rs with a delay of one instruction.

Jump And Link Register

JALR rs, rd

The program jumps to the address specified in register rs with a delay of one instruction.

The address of the instruction following the delay slot is stored into rd.

There are the following common restrictions for Tables 2-17 and 2-18.

(3) Branch address

All branch instruction target addresses are computed by adding the address of the instruction in the delay slot to

the 16-bit offset (shifted left by 2 bits and sign-extended to 64 bits). All branches occur with a delay of one

instruction.

(4) Operation when unbranched (Table 2-18)

If the branch condition does not meet in executing a likely instruction, the instruction in its delay slot is nullified.

For all other branch instructions, the instruction in its delay slot is unconditionally executed.

Remark The target instruction of the branch is fetched at the EX stage of the branch instruction. Comparison of

the operands of the branch instruction and calculation of the target address is performed at phase 2 of

the RF stage and phase 1 of the EX stage of the instruction. Branch instructions require one cycle of

the branch delay slot defined by the architecture. Jump instructions also require one cycle of delay slot.

If the branch condition is not satisfied in a branch likely instruction, the instruction in its delay slot is

nullified.

op

rs

rt

funct

rd

sa

op

target

op

target