5 a_rqu (receiving queue underrun register), 6 a_rqa (receiving queue alert register), 7 a_ver (version register) – NEC Network Controller uPD98502 User Manual

Page 242: 8 a_cmr (command register), 9 a_cer (command extension register)

CHAPTER 4 ATM CELL PROCESSOR

242

Preliminary User’s Manual S15543EJ1V0UM

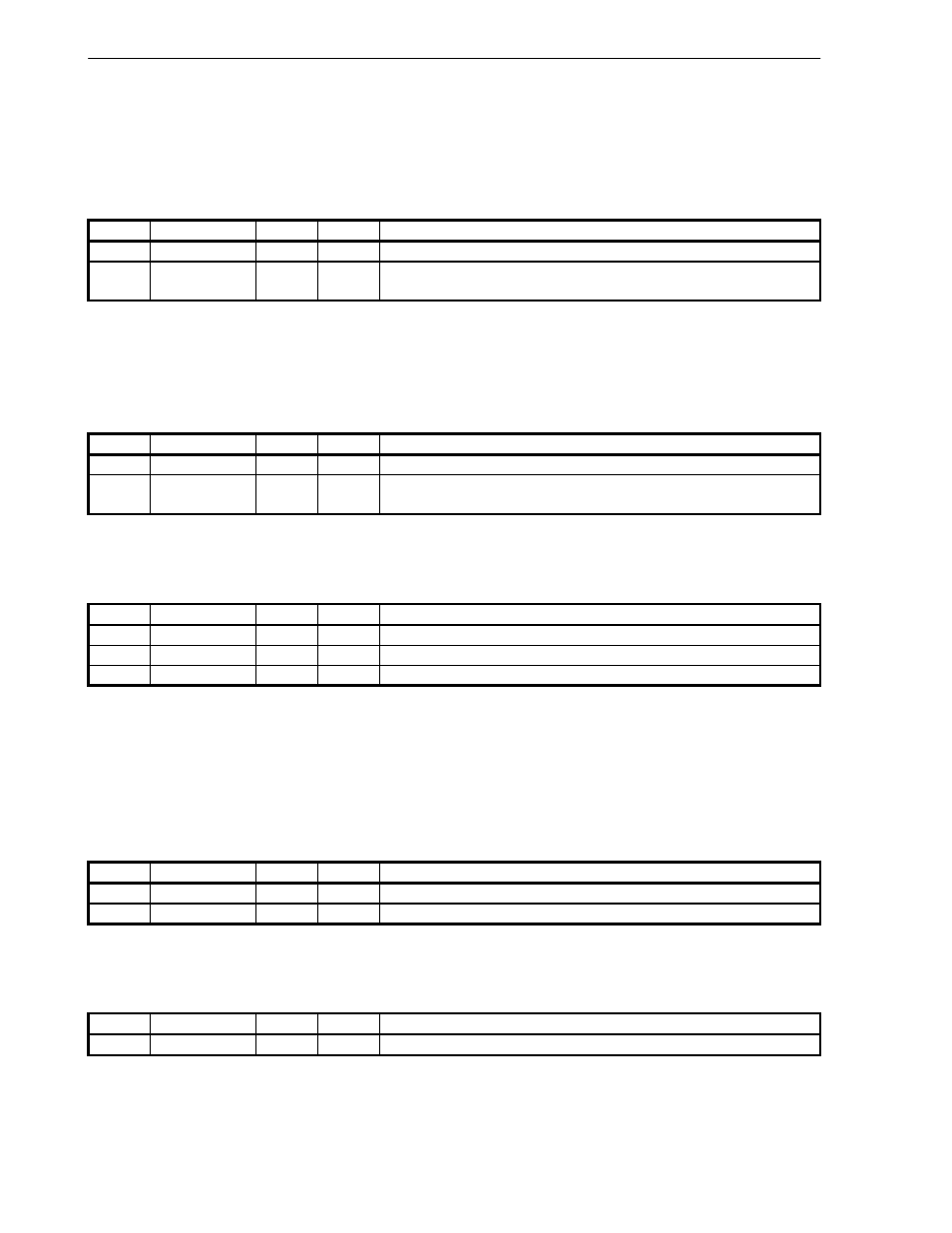

4.4.5 A_RQU (Receiving Queue Underrun Register)

A_RQU shows the status of each pool. When a pool has no free buffers, the corresponding bit is set. ATM Cell

Processor detects a pool empty when it receives a cell and try to send the cell to buffer. Whenever one of A_RQU bits

is set, A_RQU bit in A_GSR will be set. In this block, only pool7 to pool0 will be used. If a bit is set to ‘1’,

corresponding pool has no free buffers. Initial value is all zero.

Bits

Field

R/W

Default

Description

31:8

Reserved

R

0

Reserved for future use

7:0

A_RQU[7:0]

R

0

0 = pool [7:0] has free buffers

1 = pool [7:0] has no free buffers

4.4.6 A_RQA (Receiving Queue Alert Register)

A_RQA shows pools with less remaining batches than “ALERT LEVEL”, which is set by V

R

4120A. Whenever one

of A_RQA bits is set, A_RQA bit in A_GSR will be set. In this block, only pool7 to pool0 will be used. If a bit is set to

‘1’, the number of remaining batches is less than “ALERT LEVEL”. Initial value is all zero.

Bits

Field

R/W

Default

Description

31:8

Reserved

R

0

Reserved for future use

7:0

A_RQA[7:0]

R

0

0 = pool [7:0] has more or equal remaining batches than “ALERT LEVEL”

1 = pool [7:0] has less remaining batches than “ALERT LEVEL”

4.4.7 A_VER (Version Register)

A_VER shows version number of ATM Cell Processor block. Initial value is 0000_0200H.

Bits

Field

R/W

Default

Description

31:16

Reserved

R

0

Reserved for future use

15:8

MAJOR

R

02H

Major revision

7:0

MINOR

R

00H

Minor revision

4.4.8 A_CMR (Command Register)

ATM Cell Processor receives command and parameter when V

R

4120A writes them in A_CMR and A_CER. ATM

Cell Processor can handle only one command at a time. When ATM Cell Processor receives a command from

V

R

4120A, it sets Busy Flag in the register automatically to indicate it is busy. While Busy Flag is set, ATM Cell

Processor can not receive a new command. If V

R

4120A writes a new command when Busy Flag is set, the new

command will be ignored. Initial value is zero. Detail of this register is described in Section 4.7 Commands.

Bits

Field

R/W

Default

Description

31

BSY

R/W

0

Busy Flag

30:0

A_CMR

R/W

0

Command and parameter

4.4.9 A_CER (Command Extension Register)

Command Extension Register. Initial value is zero. Detail of this register is described in Section 4.7 Commands.

Bits

Field

R/W

Default

Description

31:0

A_CER

R/W

0

Parameter of command