Cache, Cache (3/4) – NEC Network Controller uPD98502 User Manual

Page 467

APPENDIX A MIPS III INSTRUCTION SET DETAILS

Preliminary User’s Manual S15543EJ1V0UM

467

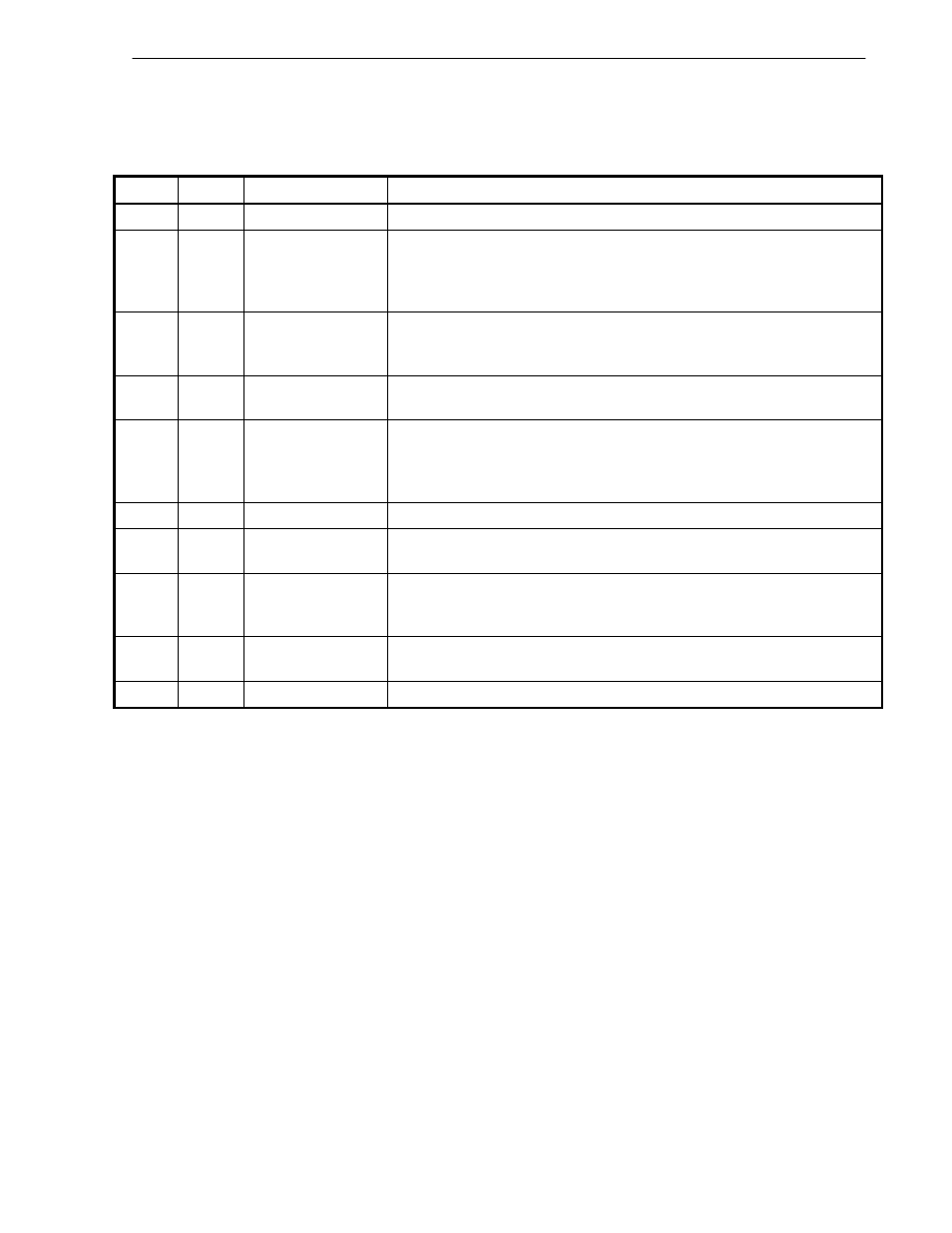

CACHE

Cache (3/4)

CACHE

Code

Cache

Name

Operation

0

I

Index_Invalidate

Set the cache state of the cache block to Invalid.

0

D

Index_Write_

Back_Invalidate

Examine the cache state and W bit of the primary data cache block at the index

specified by the virtual address. If the state is not Invalid and the W bit is set, then

write back the block to memory. The address to write is taken from the primary cache

tag. Set cache state of primary cache block to Invalid.

1

I, D

Index_Load_Tag

Read the tag for the cache block at the specified index and place it into the TagLo

CP0 registers, ignoring parity errors. Also load the data parity bits into the ECC

register.

2

I, D

Index_Store_

Tag

Write the tag for the cache block at the specified index from the TagLo and TagHi

CP0 registers.

3

D

Create_Dirty_

Exclusive

This operation is used to avoid loading data needlessly from memory when writing

new contents into an entire cache block. If the cache block does not contain the

specified address, and the block is dirty, write it back to the memory. In all cases, set

the cache state to Dirty.

4

I, D

Hit_Invalidate

If the cache block contains the specified address, mark the cache block invalid.

5

D

Hit_Write_Back

Invalidate

If the cache block contains the specified address, write back the data if it is dirty, and

mark the cache block invalid.

5

I

Fill

Fill the primary instruction cache block from memory. If the CE bit of the Status

register is set, the contents of the ECC register is used instead of the computed parity

bits for addressed doubleword when written to the instruction cache.

6

D

Hit_Write_Back

If the cache block contains the specified address, and the W bit is set, write back the

data to memory and clear the W bit.

6

I

Hit_Write_Back

If the cache block contains the specified address, write back the data unconditionally.