3 system controller, R s -2 3 2 c /m ic ro w ire – NEC Network Controller uPD98502 User Manual

Page 28

CHAPTER 1 INTRODUCTION

28

Preliminary User’s Manual S15543EJ1V0UM

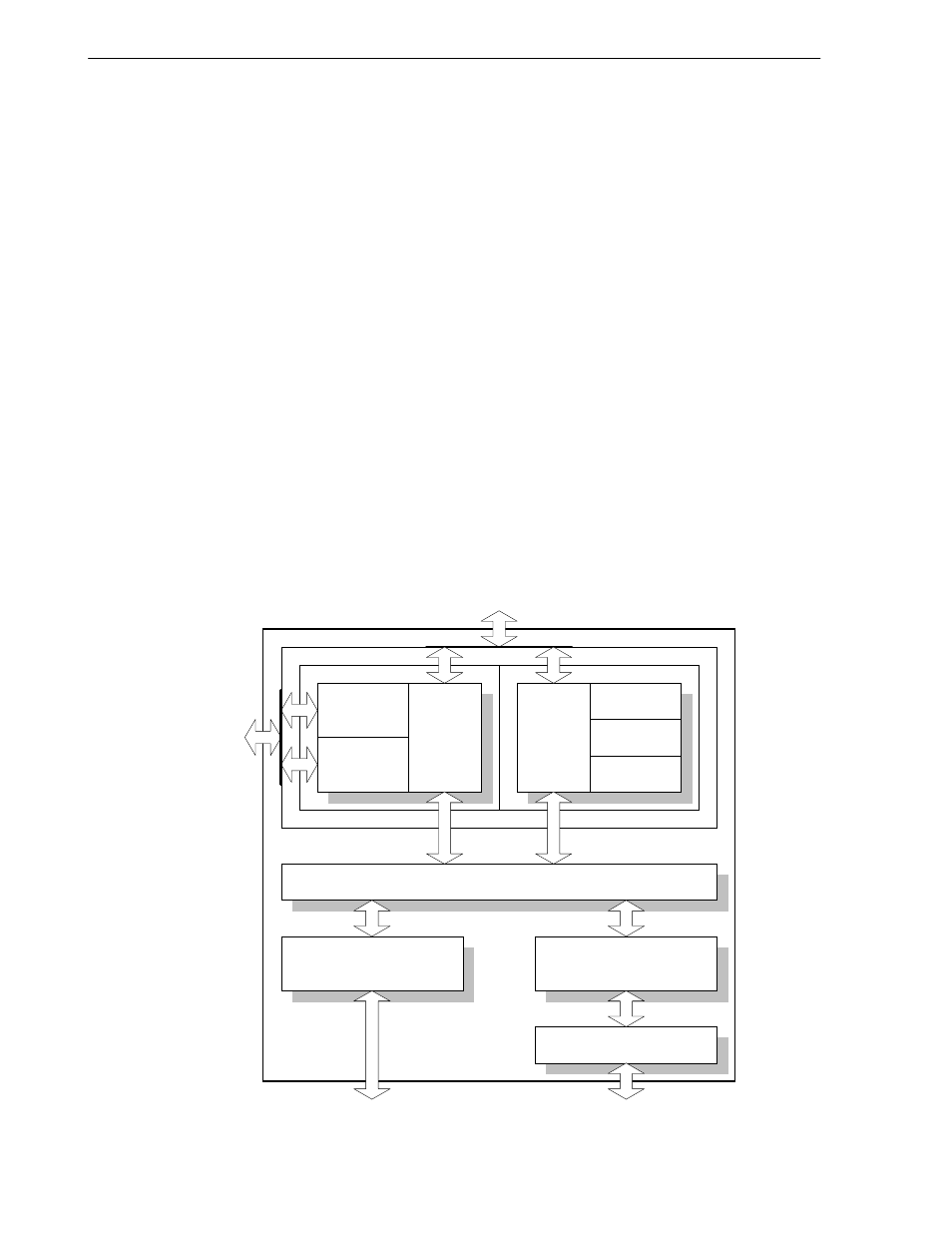

1.5.3 System controller

System Controller is

µPD98502’s internal system controller. System Controller provides bridging function among

the V

R

4120A System Bus “SysAD”, NEC original high-speed on-chip bus “IBUS” and memory bus for

SDRAM/PROM/Flash.

Features of System Controller are as follows;

• Implements 4-word prefetch FIFO buffer between SysAD and Memory

• Implements 32-bit×64-word FIFO buffer for each Tx and Rx to IBUS

• Implements 32-bit× 4-word FIFO buffer for each Tx and Rx to HBUS

• Provides bus bridging function among SysAD bus and IBUS (internal bus) and Memory

• Supports Endian Converting function on SysAD bus

• Can directly connect SDRAM (MAX. 32 MBytes) and PROM/Flash (MAX. 8 MBytes) memory

• Supports all V

R

4120A bus cycles at 66 MHz or 100 MHz

• PROM/Flash data signals multiplexed on SDRAM data signals

• Supports 266-MB/sec (32 bits @66 MHz) bursts on IBUS

• Generates NMI and INT

• Supports NS16550 compatible Universal Asynchronous Receiver/Transmitter (UART)

• Supports separated 2-ch Timer

• Supports Deadman’s Switch Unit (Watch Dog Timer)

• Supports Micro Wire interface

Figure 1-5. Block Diagram of System Controller

S y s te m C o n tro lle r

IB U S

S ys A D B U S

P H B

P B U S -H B U S B rid g e

P F U R

F A S T -U A R T

H A R B

H B U S A rb ite r

IH B

IB U S -H B U S B rid g e

F la s h

P R O M

S D R A M

R S -2 3 2 C /M ic ro W ire

H B U S

H B U S

H B U S

P B U S

R O M -IF

S D R A M -IF

S y s te m

B rid g e

M e m o ry

A rb ito r

H B U S

M IF

H IF

V R IF

D S U

T IM E R

R E G IS T E R