6 i/o performance – NEC Network Controller uPD98502 User Manual

Page 203

CHAPTER 3 SYSTEM CONTROLLER

Preliminary User’s Manual S15543EJ1V0UM

203

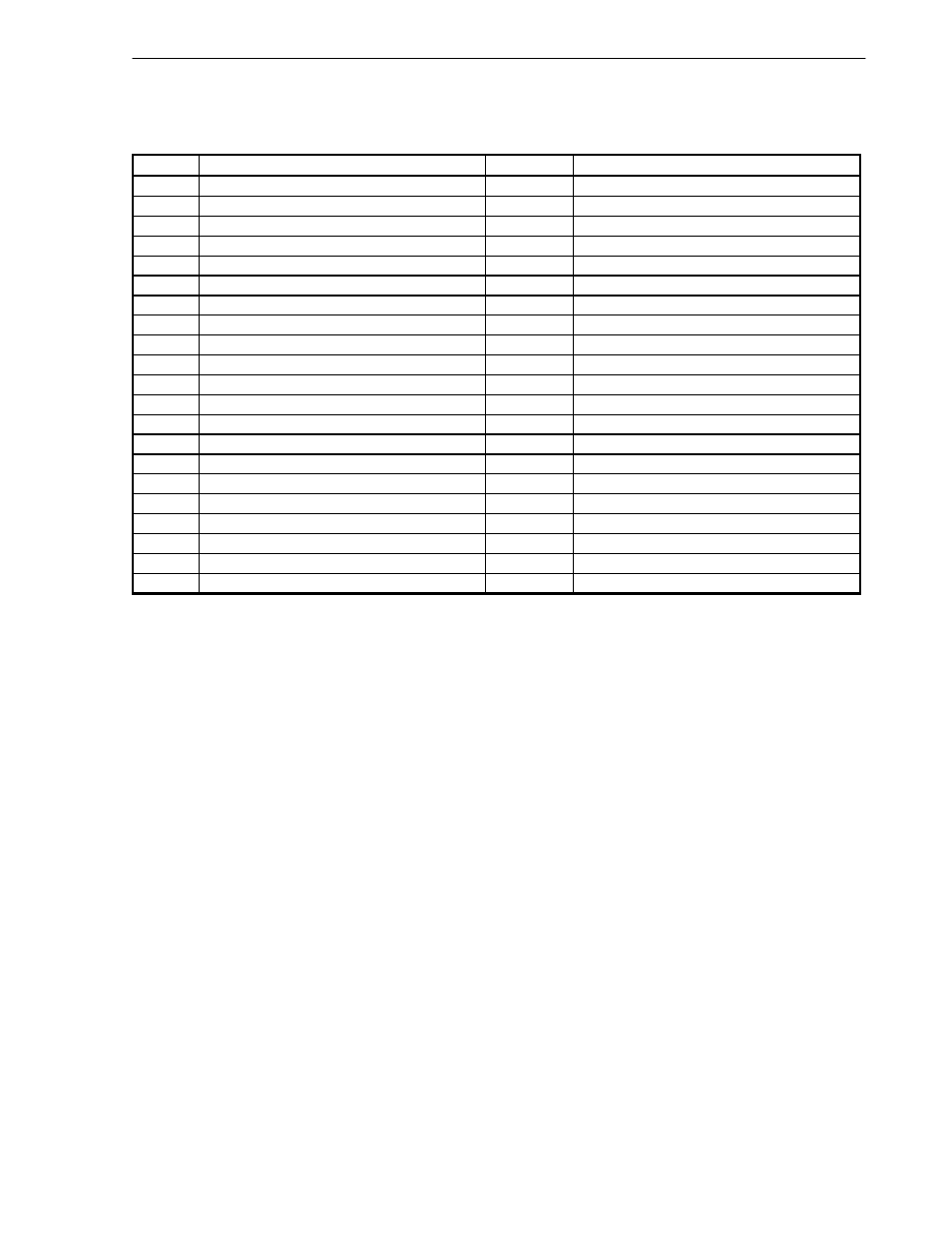

3.3.6 I/O performance

The following table indicates the I/O performance accessing from the V

R

4120A through the system controller.

W/R

Target area

Burst length

Access latency [V

R

4120A clocks]

R

IBUS target

1

24

R

IBUS target

2

24-1

R

IBUS target

4

27-1-1-1

R

Internal register (except UART)

1

7

R

Internal register (except UART)

2

Invalid

R

Internal register (except UART)

4

Invalid

R

Internal UART register

1

14 (depend UART source clock)

R

Internal UART register

2

Invalid

R

Internal UART register

4

Invalid

W

IBUS target

1

23

W

IBUS target

2

23

W

IBUS target

4

23-2-1-2

W

Internal write command FIFO

1

6-1(wait)

W

Internal write command FIFO

2

6-1

W

Internal write command FIFO

4

6-1-1-1

W

Internal register (except UART)

1

7

W

Internal register (except UART)

2

Invalid

W

Internal register (except UART)

4

Invalid

W

Internal UART register

1

15 (depend UART source clock)

W

Internal UART register

2

Invalid

W

Internal UART register

4

Invalid

Remarks 1. BUS frequency: SysAD = 100 MHz , IBUS = 66 MHz

2. The latency value accessing to the IBUS target does not include IBUS bus arbitration cycle (about 6

CPU clocks).