A.2 load and store instructions – NEC Network Controller uPD98502 User Manual

Page 433

APPENDIX A MIPS III INSTRUCTION SET DETAILS

Preliminary User’s Manual S15543EJ1V0UM

433

(1) Instruction notation examples

The following examples illustrate the application of some of the instruction notation conventions:

Example 1:

GPR [rt]

← immediate || 0

16

Sixteen zero bits are concatenated with an immediate value (typically 16 bits), and the 32-bit string is

assigned to general register

rt.

Example 2:

(immediate15)

16

|| immediate15...0

Bit 15 (the sign bit) of an immediate value is extended for 16-bit positions, and the result is concatenated

with bits 15 through 0 of the immediate value to form a 32-bit sign extended value.

A.2 Load and Store Instructions

In the V

R

4120A CPU implementation, the instruction immediately following a load may use the loaded contents of

the register. In such cases, the hardware interlocks, requiring additional real cycles, so scheduling load delay slots is

still desirable, although not required for functional code.

In the load and store descriptions, the functions listed in Table A-2 are used to summarize the handling of virtual

addresses and physical memory.

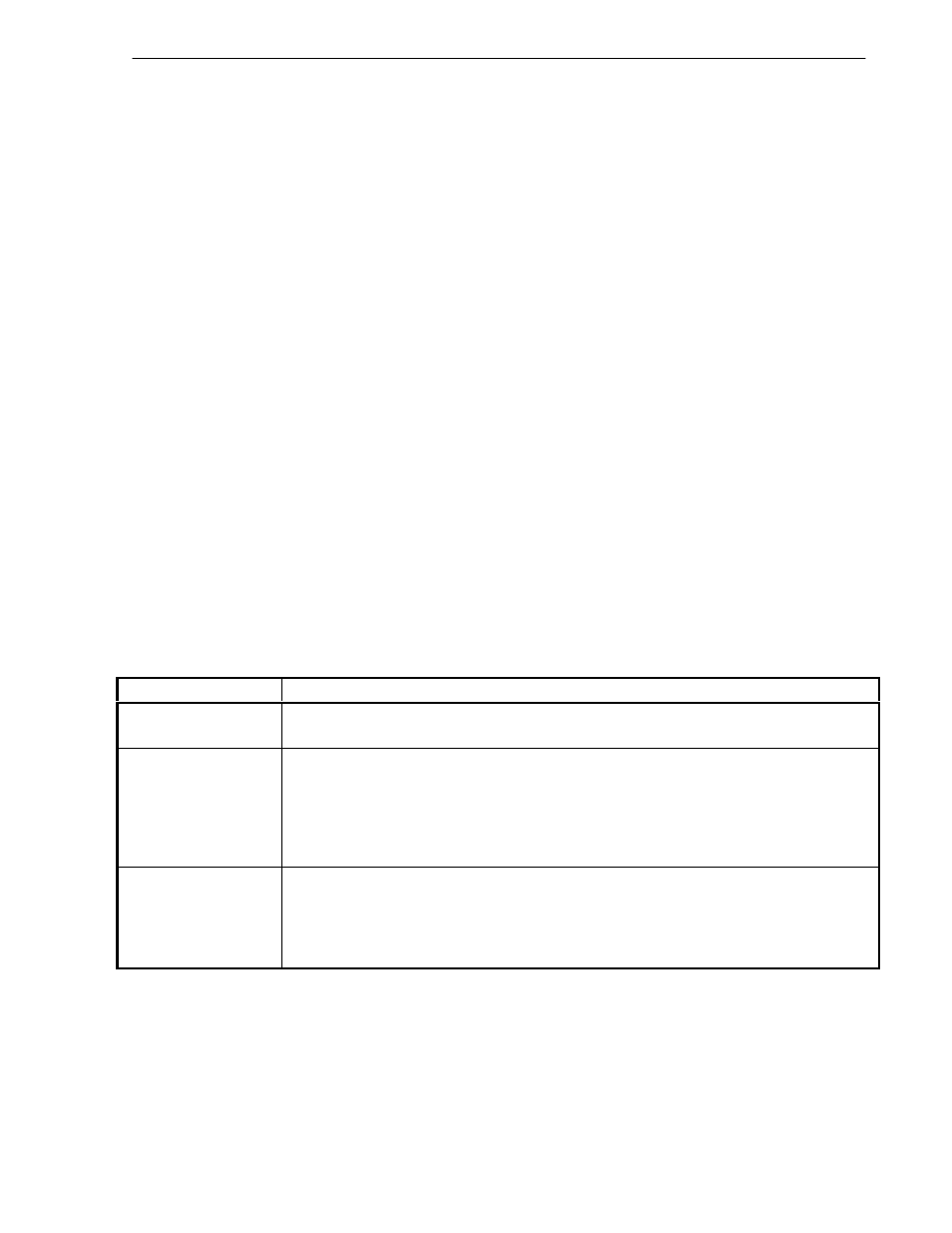

Table A-2. Load and Store Common Functions

Function

Description

AddressTranslation

Uses the TLB to find the physical address given the virtual address. The function fails and an exception

is taken if the required translation is not present in the TLB.

LoadMemory

Uses the cache and main memory to find the contents of the word containing the specified physical

address. The low-order three bits of the address and the Access Type field indicate which of each of the

four bytes within the data word need to be returned. If the cache is enabled for this access, the entire

word is returned and loaded into the cache. If the specified data is short of word length, the data position

to which the contents of the specified data is stored is determined considering the endian mode and

reverse endian mode.

StoreMemory

Uses the cache, write buffer, and main memory to store the word or part of word specified as data in the

word containing the specified physical address. The low-order three bits of the address and the Access

Type field indicate which of each of the four bytes within the data word should be stored. If the specified

data is short of word length, the data position to which the contents of the specified data is stored is

determined considering the endian mode and reverse endian mode.