6 initialization, 1 before starting risc core – NEC Network Controller uPD98502 User Manual

Page 255

CHAPTER 4 ATM CELL PROCESSOR

Preliminary User’s Manual S15543EJ1V0UM

255

4.6 Initialization

This ATM Cell Processor is initialized by firmware that is based RISC instruction.

4.6.1 Before starting RISC core

RISC Core has 1 MB of Instruction space and 8 KB of physical Instruction RAM and 8 KB of instruction cache. The

Instruction space will be mapped to the external system memory space. Address of instruction space will be translated

by adding content of A_INBAR. V

R

4120A will set A_INBAR during initialization. Instruction memory space will be

placed in the system memory space to achieve faster instruction fetch. V

R

4120A has to transfer RISC Core F/W to the

assigned SDRAM area as well as its own S/W in its initialization, as shown in Figure 4-16. After transferring F/W, it

sets base address of RISC Core F/W in A_INBAR. At the same time, base address of shared memory space has to

be set in A_IBBAR. Then V

R

4120A let ATM Cell Processor to start operation.

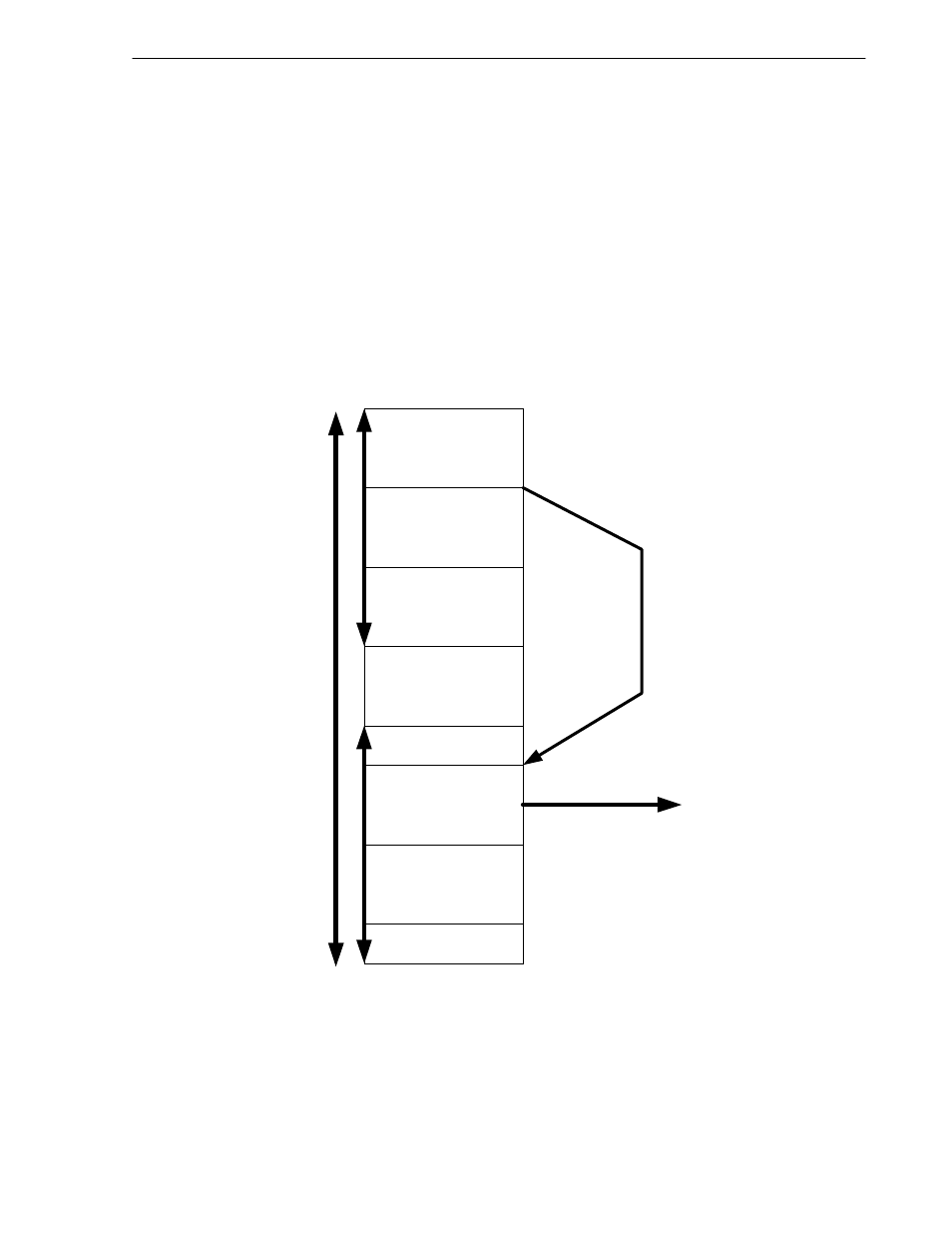

Figure 4-16. Transfer of F/W

µ

P D 98502 M /W &

R T O S

A T M C ell

P rocessing F /W

RO

M

S

p

a

c

e

A T M C ell

P rocessing F /W

(copy)

2. R IS C C ore

fetches

instructions

1. transfers

F /W to

S D R A M

µ

P D 98502 M /W &

R T O S

(copy)

µ

P

D

98

50

2 M

e

m

o

ry

S

p

ac

e

S

DRA

M

S

p

a

c

e