3 tm0csr (timer ch0 count set register), 4 tm1csr (timer ch1 count set register), 5 tm0ccr (timer ch0 current count register) – NEC Network Controller uPD98502 User Manual

Page 426: 6 tm1ccr (timer ch1 current count register)

CHAPTER 9 TIMER

426

Preliminary User’s Manual S15543EJ1V0UM

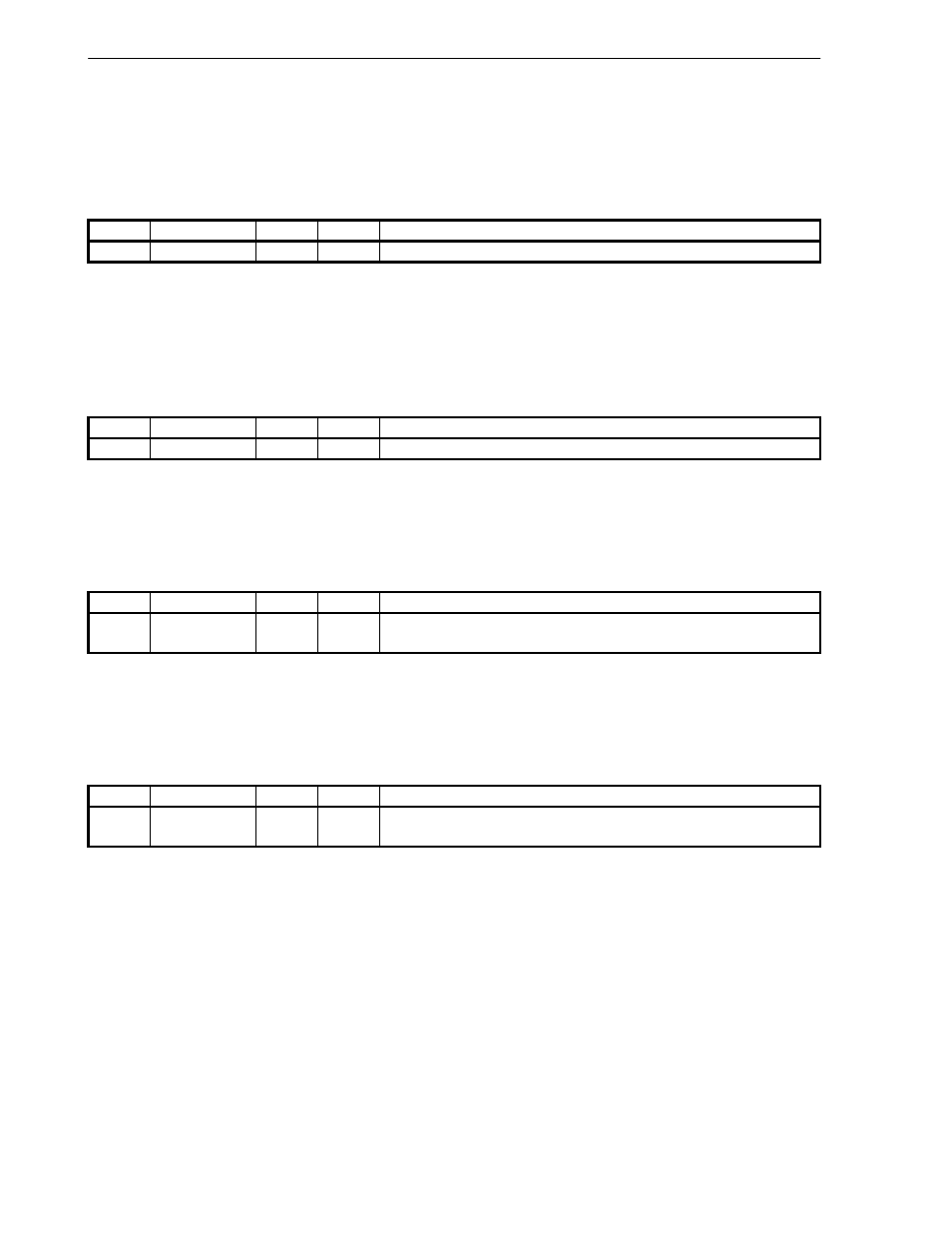

9.3.3 TM0CSR (Timer CH0 Count Set Register)

The Timer CH0 Count Set Register “TM0CSR” is a read-write and 32-bit word-aligned register. CPU (V

R

4120A)

loads a value in it and the counter starts counting down from the (TM0CSR –1) value. When it reaches 0000_0000H,

it generates an interrupt to the CPU via Interrupt Status Register “ISR” if the TM0IS in ISR is not masked by TM0IM in

IMR. TM0CSR is initialized to 0 at reset and contains the following field:

Bits

Field

R/W

Default

Description

31:0

TM0SET

R/W

0

Initial and Reload Value for Timer CH0

9.3.4 TM1CSR (Timer CH1 Count Set Register)

The Timer CH1 Count Set Register “TM1CSR” is a read-write and 32-bit word-aligned register. CPU (V

R

4120A)

loads a value in it and the counter starts counting down from the (TM1CSR –1) value. When it reaches 0000_0000H,

it generates an interrupt to the CPU via Interrupt Status Register “ISR” if the TM1IS in ISR is not masked by TM1IM in

IMR. TM1CSR is initialized to 0 at reset and contains the following field:

Bits

Field

R/W

Default

Description

31:0

TM1SET

R/W

0

Initial and Reload Value for Timer CH1

9.3.5 TM0CCR (Timer CH0 Current Count Register)

The Timer CH0 Current Count Register “TM0CCR” is read-only and 32-bit word-aligned register. CPU (V

R

4120A)

can read its value to get timer CH0 current count. TM0CSR is initialized to FFFF_FFFFH at reset and contains the

following field:

Bits

Field

R/W

Default

Description

31:0

TM0CNT

R

FFFF_

FFFFH

Timer CH0 Current Count Value

9.3.6 TM1CCR (Timer CH1 Current Count Register)

The Timer CH1 Current Count Register “TM1CCR” is read-only and word aligned 32bit register. CPU (V

R

4120A)

can read its value to get timer CH1 current count. TM1CCR is initialized to FFFF_FFFFH at reset and contains the

following fields:

Bits

Field

R/W

Default

Description

31:0

TM1CCR

R

FFFF_

FFFFH

Timer CH1 Current Count Value