11 p_pimr (pci interrupt mask register) – NEC Network Controller uPD98502 User Manual

Page 397

CHAPTER 7 PCI CONTROLLER

Preliminary User’s Manual S15543EJ1V0UM

397

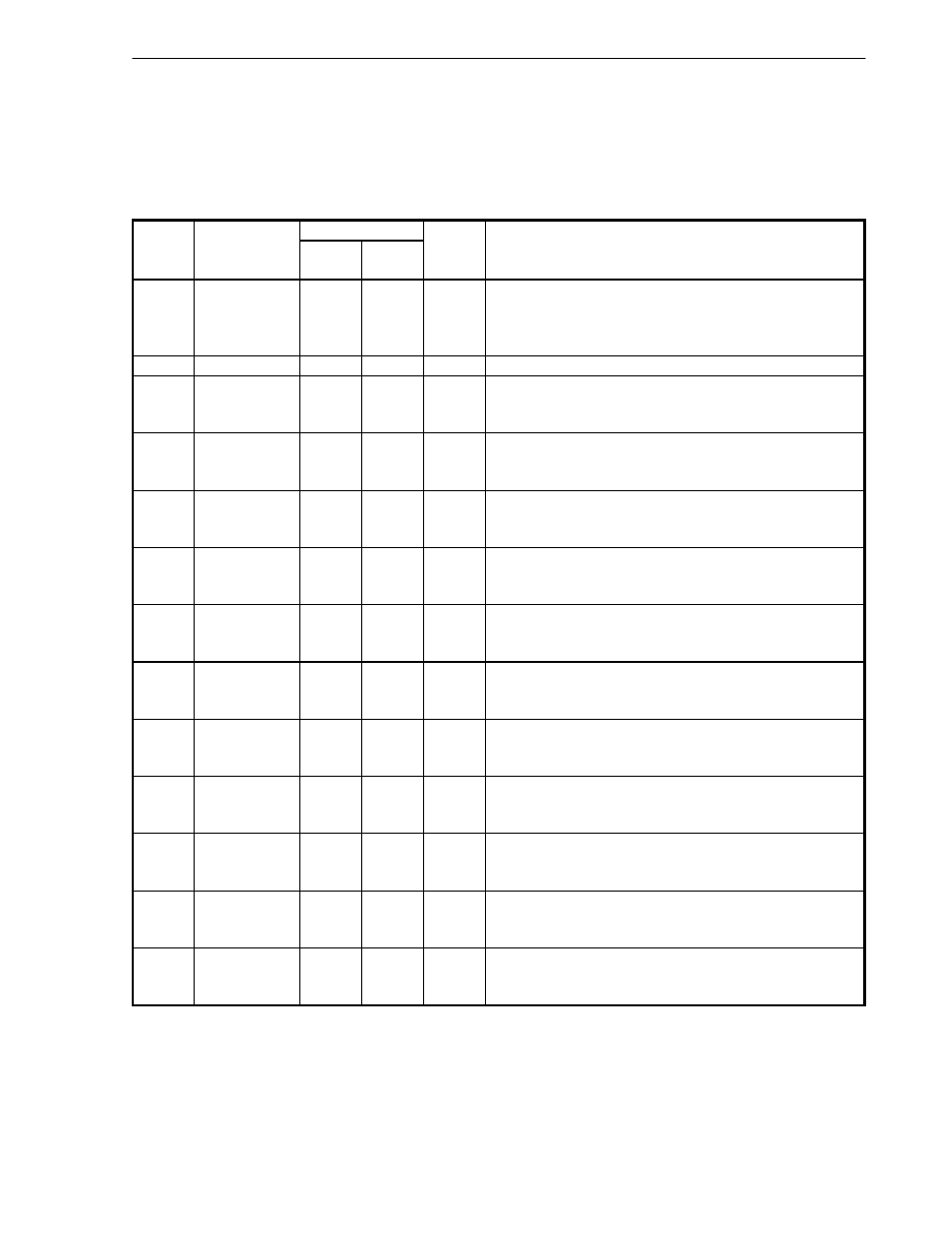

7.5.11 P_PIMR (PCI Interrupt Mask Register)

PIMR register masks interruptions. A mask bit, which locates in the same bit position to a corresponding bit in

PGSR, can mask the interruption. When a bit of this register is reset to ‘0’, the corresponding bit of the PGSR is

masked. When it is set to ‘1’, the corresponding bit is unmasked. When the mask bit is reset and the bit in PGSR is

set, the PCI Controller sets the interrupt signal to PCI-Host.

R/W

Bits

Field

Internal

bus

PCI

Default

Description

31:16

PUINT

R/W

R/W

0

Mask bits for the Interrupts defined by the system the chip is

used.

‘0’ means masked.

‘1’ means unmasked.

15:11

Reserved

-

-

0

Hardwired to ‘0’s.

10

IPREQ

R/W

R/W

0

Mask bit for the state transition for PPMI.

‘0’ means masked.

‘1’ means unmasked.

9

SWRDN

R/W

R/W

0

Mask bit for Software Reset done.

‘0’ means masked.

‘1’ means unmasked.

8

DPERR

R/W

R/W

0

Mask bit for Detected Parity Error.

‘0’ means masked.

‘1’ means unmasked.

7

SSERR

R/W

R/W

0

Mask bit for Signaled SERR_B.

‘0’ means masked.

‘1’ means unmasked.

6

RMABT

R/W

R/W

0

Mask bit for Received Master Abort.

‘0’ means masked.

‘1’ means unmasked.

5

RTABT

R/W

R/W

0

Mask bit for Received Target Abort.

‘0’ means masked.

‘1’ means unmasked.

4

STABT

R/W

R/W

0

Mask bit for Signaled Target Abort.

‘0’ means masked.

‘1’ means unmasked.

3

PFDSC

R/W

R/W

0

Mask bit for the discard of data in PCI FIFO.

‘0’ means masked.

‘1’ means unmasked.

2

RTYTE

R/W

R/W

0

Mask bit for Retry Timer Expired.

‘0’ means masked.

‘1’ means unmasked.

1

PRBER

R/W

R/W

0

Mask bit for internal bus Error in read transaction.

‘0’ means masked.

‘1’ means unmasked.

0

PWBER

R/W

R/W

0

Mask bit for internal bus Error in write transaction.

‘0’ means masked.

‘1’ means unmasked.