2 uartrbr (uart receiver data buffer register), 3 uartthr (uart transmitter data holding register), 4 uartier (uart interrupt enable register) – NEC Network Controller uPD98502 User Manual

Page 416: 5 uartdll (uart divisor latch lsb register)

CHAPTER 8 UART

416

Preliminary User’s Manual S15543EJ1V0UM

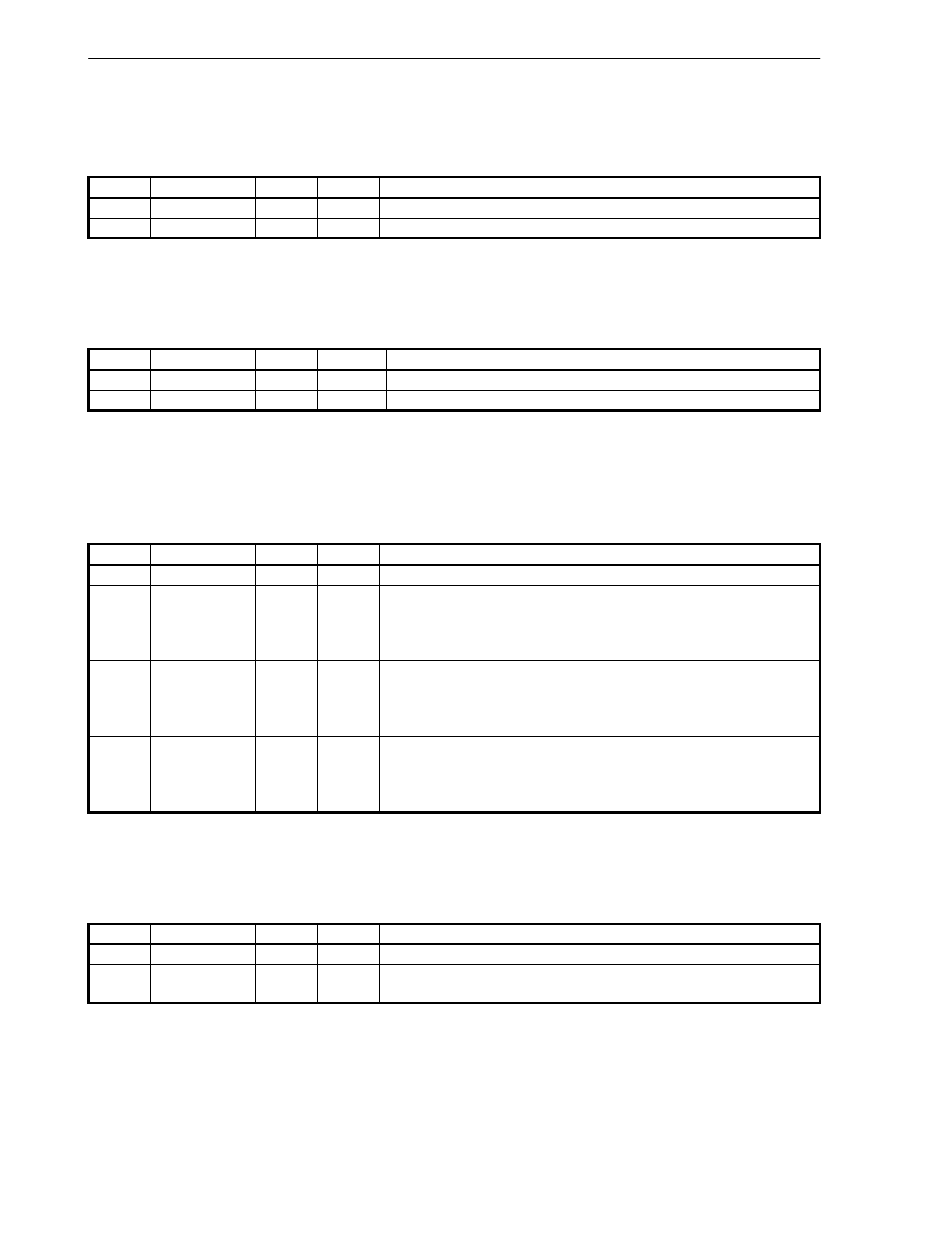

8.3.2 UARTRBR (UART Receiver data Buffer Register)

This register holds receive data. It is only accessed when the Divisor Latch Access bit (DLAB) is cleared in the

UARTLCR.

Bits

Field

R/W

Default

Description

31:8

Reserved

R

0

Hardwired to 0.

7:0

UDATA

R

-

UART receive data (read only) when DLAB = 0.

8.3.3 UARTTHR (UART Transmitter data Holding Register)

This register holds transmit data. It is only accessed when the Divisor Latch Access bit (DLAB) is cleared in the

UARTLCR.

Bits

Field

R/W

Default

Description

31:8

Reserved

W

0

Hardwired to 0.

7:0

UDATA

W

-

UART transmit data (write only) when DLAB = 0.

8.3.4 UARTIER (UART Interrupt Enable Register)

This register is used to enable UART interrupts. It is only accessed when the Divisor Latch Access bit (DLAB) is set

in the UARTLCR. The UARTIM (bit2 in Interrupt Mask Register “S_IMR”) is a global enable for interrupt sources

enabled by this register.

Bits

Field

R/W

Default

Description

31:4

Reserved

R/W

0

Hardwired to 0.

3

ERBMI

R/W

0

UART Modem status Interrupts:

1 = Enable Modem status change interrupt

0 = Disable such interrupts

Modem status changes are reported to UARTMSR

2

ERBLI

R/W

0

UART Line status Interrupts:

1 = Enable Line status error interrupt

0 = Disable such interrupts

Line status error interrupt state reported to UARTLSR

1

ERBEI

R/W

0

UART Transmitter Buffer empty Interrupt:

1 = Enable Transmitter Buffer empty interrupt

0 = Disable such interrupts

Transmitter Buffer empty state reported to UARTLSR

8.3.5 UARTDLL (UART Divisor Latch LSB Register)

This register is used to set the divisor (division rate) for the baud rate generator. The data in this register and the

lower 8-bit data in UARTDLM register are together handled as 16-bit data.

Bits

Field

R/W

Default

Description

31:8

Reserved

R/W

0

Hardwired to 0.

7:0

DIVLSB

R/W

-

UART divisor latch (see Table 8-1):

Only accessed when DLAB = 1 in UARTLCR