2 precision of exceptions, 3 exception processing registers – NEC Network Controller uPD98502 User Manual

Page 130

CHAPTER 2 V

R

4120A

130

Preliminary User’s Manual S15543EJ1V0UM

2.5.2 Precision of exceptions

V

R

4120A CPU exceptions are logically precise; the instruction that causes an exception and all those that follow it

are aborted and can be re-executed after servicing the exception. When succeeding instructions are discarded,

exceptions associated with those instructions are also discarded. Exceptions are not taken in the order detected, but

in instruction fetch order.

The exception handler can determine the cause of an exception and the address. The program can be restarted

by rewriting the destination register - not automatically, however, as in the case of all the other precise exceptions

where no status change occurs.

2.5.3 Exception processing registers

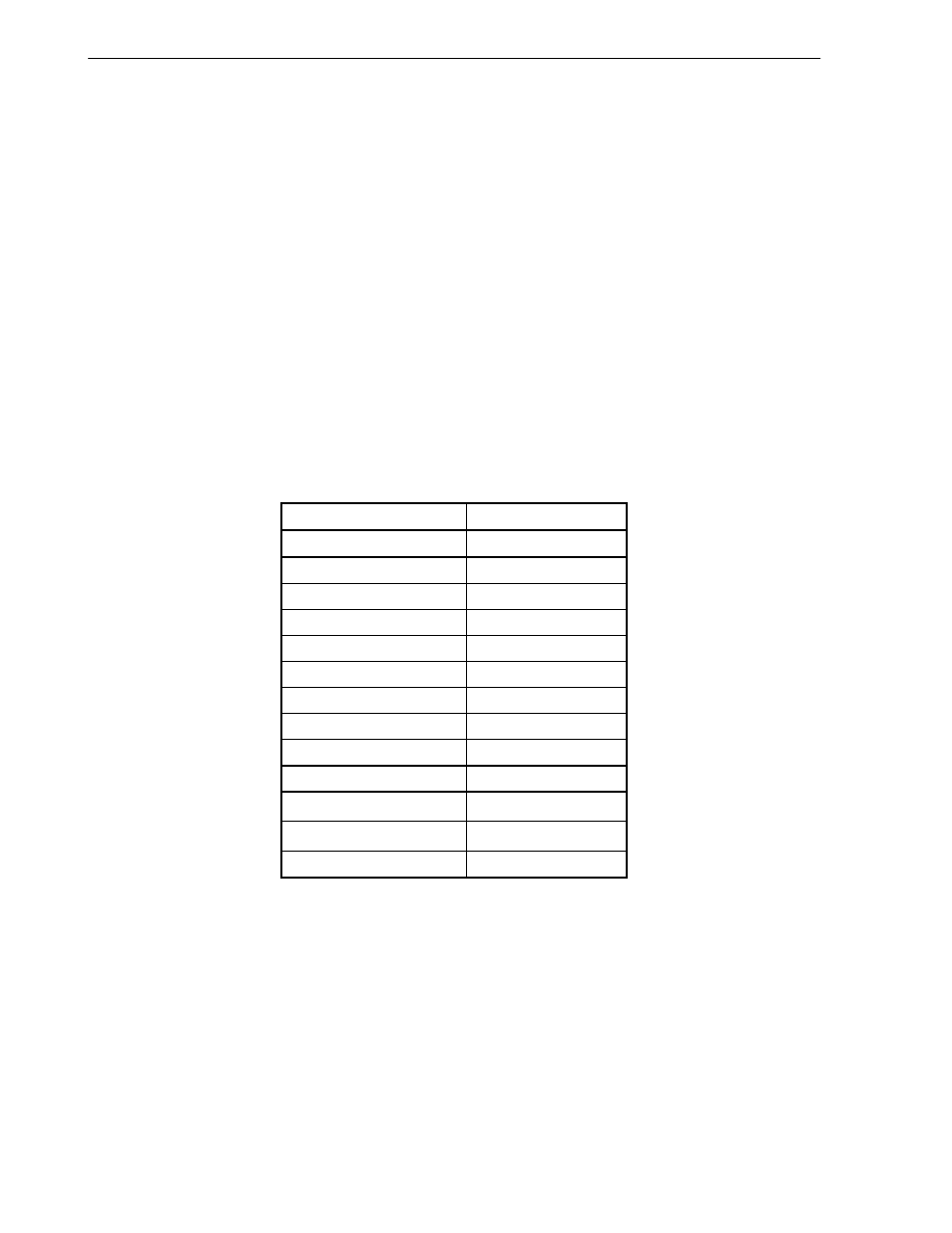

This section describes the CP0 registers that are used in exception processing. Table 2-34 lists these registers,

along with their number-each register has a unique identification number that is referred to as its register number.

The CP0 registers not listed in the table are used in memory management (for details, see Section 2.4 Memory

Management System).

The exception handler examines the CP0 registers during exception processing to determine the cause of the

exception and the state of the CPU at the time the exception occurred.

The registers in Table 2-34 are used in exception processing, and are described in the sections that follow.

Table 2-34. CP0 Exception Processing Registers

Register Name

Register Number

Context register

4

BadVAddr register

8

Count register

9

Compare register

11

Status register

12

Cause register

13

EPC register

14

WatchLo register

18

WatchHi register

19

XContext register

20

Parity Error register

Note

26

Cache Error register

Note

27

Error EPC register

30

Note

This register is prepared to maintain

compatibility with the V

R

4100. This register is

not used in the

µPD98502 hardware.