22 u_rp2ir (usb rx pool2 information register), 23 u_rp2ar (usb rx pool2 address register), 24 u_tmsa (usb tx mailbox start address register) – NEC Network Controller uPD98502 User Manual

Page 328: 25 u_tmba (usb tx mailbox bottom address register), 26 u_tmra (usb tx mailbox read address register)

CHAPTER 6 USB CONTROLLER

328

Preliminary User’s Manual S15543EJ1V0UM

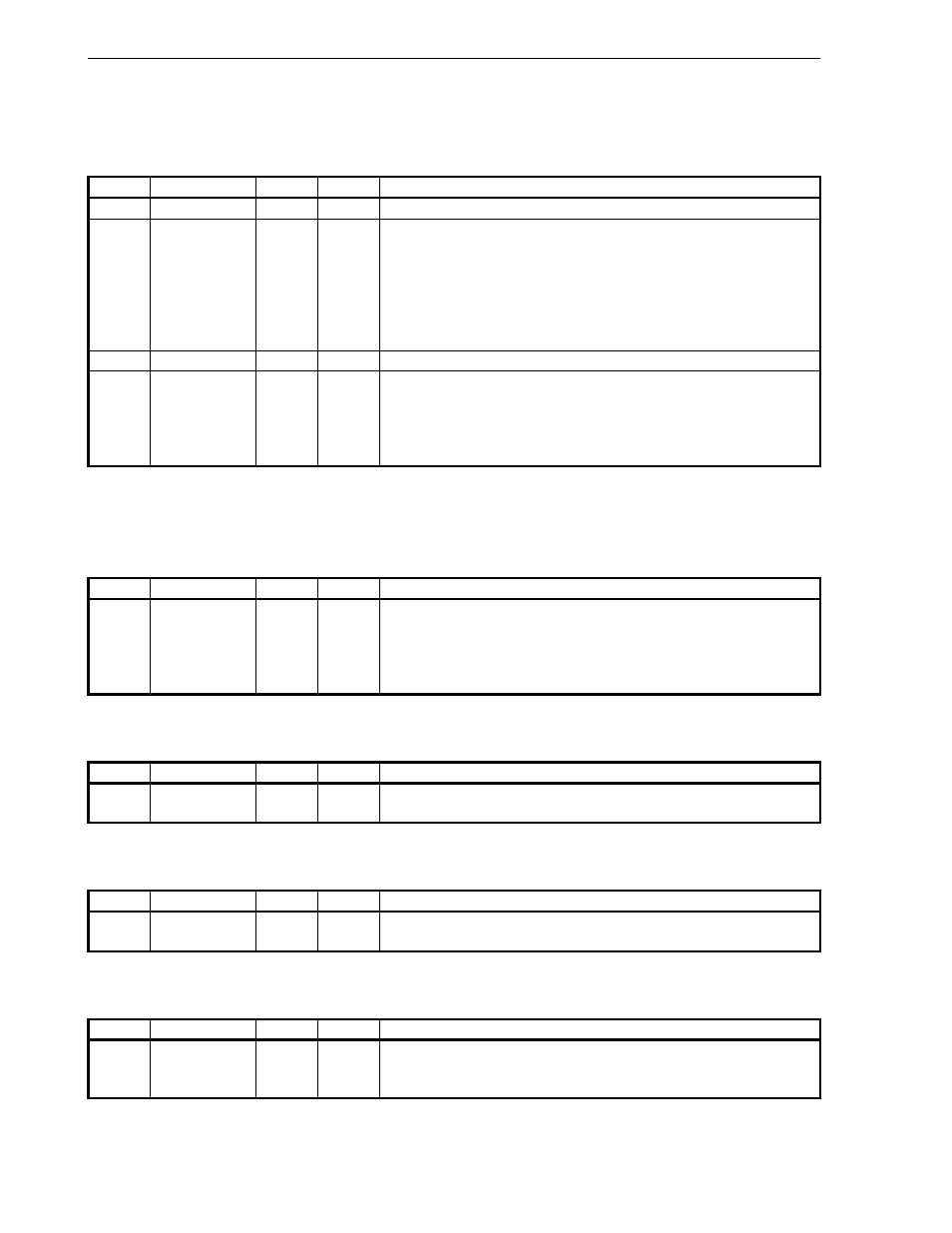

6.2.22 U_RP2IR (USB Rx Pool2 Information Register)

This register indicates the information of Receive Pool2.

The V

R

4120A writes to this register only when the device is being initialized.

Bits

Field

R/W

Default

Description

31

Reserved

R/W

0

Reserved for future use. Writes ‘0’s.

30:28

AL

R/W

000

Alert Level:

Sets the warning level for Pool0. When the number of Buffer Directories

remaining in this pool equals the value set in this field, USB Controller sets

the RPA2 bit in the USB General Status Register1 to a ‘1’.

Writing N in this field is equivalent to specifying N x 4 (remaining number of

Buffer Directories = 4, 8, 12, …, 28). When 000 is written into this field, this

function is disabled and no notification is posted to the V

R

4120A.

27:16

Reserved

R/W

0

Reserved for future use. Writes ‘0’s.

15:0

RNOD

R

0

Remaining Number of Buffer Directory:

Indicates the number of Buffer Directories remaining in Pool2. The V

R

4120A

can only read this field.

Buffer Directory addition is performed entirely using the USB Command

Register.

6.2.23 U_RP2AR (USB Rx Pool2 Address Register)

This register indicates the start address of Buffer Directory which is currently used.

The way to set up Rx Pool is described at Section 6.6.3 Receive pool settings.

Bits

Field

R/W

Default

Description

31:0

Address

R

0

Buffer Directory Address:

Register that indicates the start address of the first Buffer Directory in Pool2.

The V

R

4120A can only read this register.

Buffer Directory addition is performed entirely using the USB Command

Register.

6.2.24

U_TMSA (USB Tx MailBox Start Address Register)

Bits

Field

R/W

Default

Description

31:0

Address

R/W

0

Register that indicates the start address of the transmit MailBox area. The

V

R

4120A must set a value in this field only at initialization.

6.2.25 U_TMBA (USB Tx MailBox Bottom Address Register)

Bits

Field

R/W

Default

Description

31:0

Address

R/W

0

Register that indicates the end address of the transmit MailBox area. The

V

R

4120A must set a value in this field only at initialization.

6.2.26 U_TMRA (USB Tx MailBox Read Address Register)

Bits

Field

R/W

Default

Description

31:0

Address

R/W

0

Register that indicates the address of the area that will be read next by the

V

R

4120A. After the V

R

4120A reads the contents of a MailBox, the value set in

this register must be changed by V

R

4120A.