Mfc0, Move from system control coprocessor – NEC Network Controller uPD98502 User Manual

Page 527

APPENDIX A MIPS III INSTRUCTION SET DETAILS

Preliminary User’s Manual S15543EJ1V0UM

527

MFC0

Move From System Control Coprocessor

MFC0

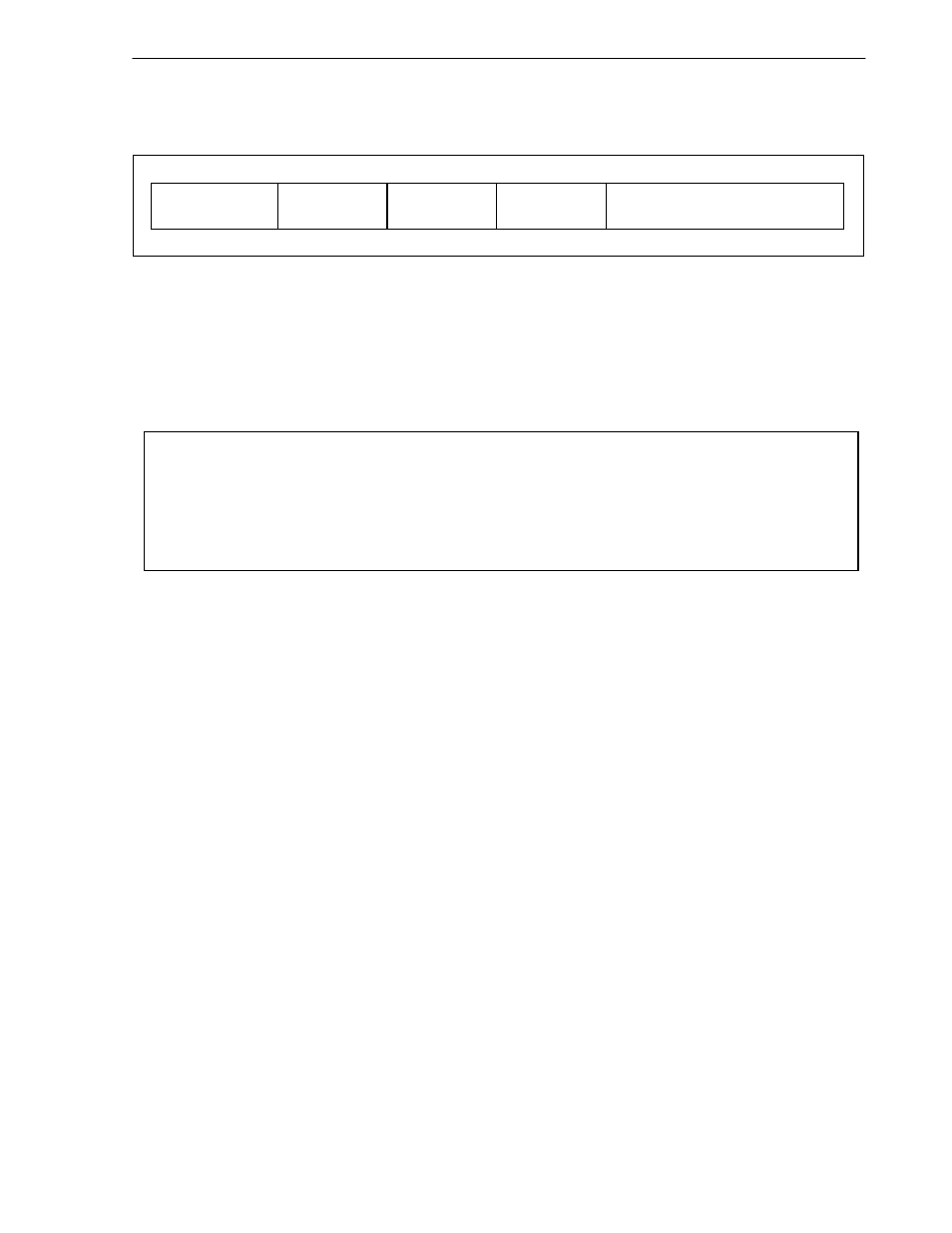

MF

0 0 0 0 0

COP0

0 1 0 0 0 0

rt

0

0 0 0 0 0 0 0 0 0 0 0

31

26 25

21 20

16 15

0

6

5

5

5

11 10

11

rd

Format:

MFC0 rt, rd

Description:

The contents of coprocessor register

rd of the CP0 are loaded into general register rt.

Operation:

32

T:

data

← CPR [0, rd]

T+1: GPR [rt]

← data

64

T:

data

← CPR [0, rd]

T+1: GPR [rt]

← (data

31

)

32

|| data

31...0

Exceptions:

Coprocessor unusable exception (in 64-bit/32-bit user and supervisor mode if CP0 not enabled)