25 en_cam2 (carry register 2 mask register), 26 en_txcr (transmit configuration register) – NEC Network Controller uPD98502 User Manual

Page 294

CHAPTER 5 ETHERNET CONTROLLER

294

Preliminary User’s Manual S15543EJ1V0UM

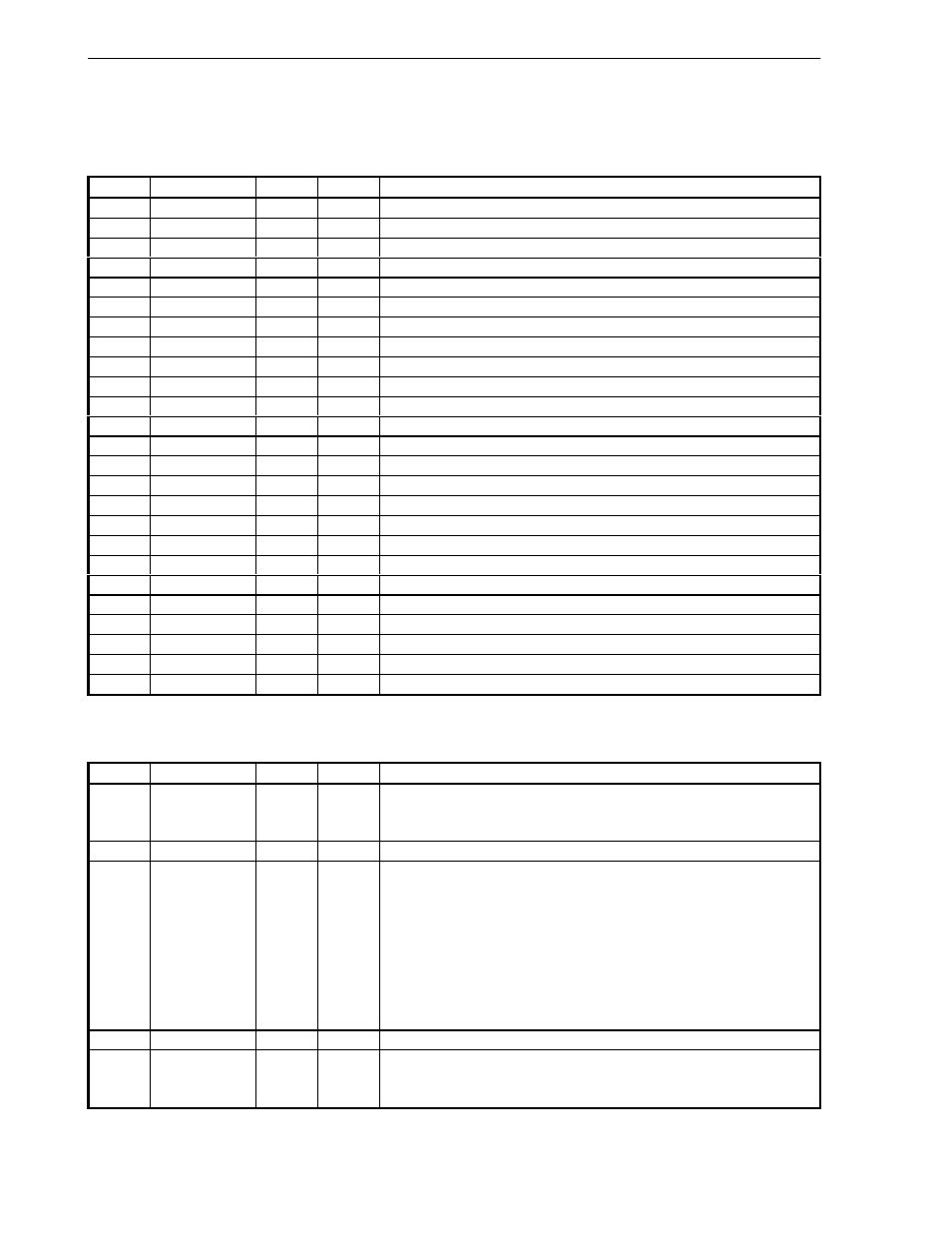

5.2.25 En_CAM2 (Carry Register 2 Mask Register)

This register masks the Interrupt that is generated from the setting of the bits in the En_CAR2 register.

Each mask bit can be enabled independently.

Bits

Field

R/W

Default

Description

31

M2XD

R/W

0

Status vector overrun mask bit

30:23

Reserved

R/W

0

Reserved for future use. Write 0s.

22

M2IM

R/W

0

En_TIME counter carry mask bit

21

M2CS

R/W

0

En_TCSE counter carry mask bit

20

M2BC

R/W

0

En_TNCL counter carry mask bit

19

M2XC

R/W

0

En_TXCL counter carry mask bit

18

M2LC

R/W

0

En_TLCL counter carry mask bit

17

M2MC

R/W

0

En_TMCL counter carry mask bit

16

M2SC

R/W

0

En_TSCL counter carry mask bit

15

M2XD

R/W

0

En_TXDF counter carry mask bit

14

M2DF

R/W

0

En_TDFR counter carry mask bit

13

M2XF

R/W

0

En_TXPF counter carry mask bit

12

M2TE

R/W

0

En_TFCS counter carry mask bit

11

M2JB

R/W

0

En_RJBR counter carry mask bit

10

M2FG

R/W

0

En_RFRG counter carry mask bit

9

M2OV

R/W

0

En_ROVR counter carry mask bit

8

M2UN

R/W

0

En_RUND counter carry mask bit

7

M2FC

R/W

0

En_RFCR counter carry mask bit

6

M2CD

R/W

0

En_RCDE counter carry mask bit

5

M2FO

R/W

0

En_RFLR counter carry mask bit

4

M2AL

R/W

0

En_RALN counter carry mask bit

3

M2UO

R/W

0

En_RXUO counter carry mask bit

2

M2PF

R/W

0

En_RXPF counter carry mask bit

1

M2CF

R/W

0

En_RXCF counter carry mask bit

0

M2RE

R/W

0

En_RFCS counter carry mask bit

5.2.26 En_TXCR (Transmit Configuration Register)

Bits

Field

R/W

Default

Description

31

TXE

R/W

0

Transmit Enable:

0: Disable

1: Enable

30:19

Reserved

R/W

0

Reserved for future use. Write 0s.

18:16

DTBS

[2:0]

R/W

0

DMA Transmit Burst Size:

000: 1 Word (4 bytes)

001: 2 Words (8 bytes)

010: 4 Words (16 bytes)

011: 8 Words (32 bytes)

100: 16 Words (64 bytes)

101: 32 Words (128 bytes)

110: 64 Words (256 bytes)

111: Reserved for future use

15:1

Reserved

R/W

0

Reserved for future use. Write 0s.

0

AFCE

R/W

0

Auto Flow Control Enable:

0: Disable

1: Enable