2 pci to internal bus transaction – NEC Network Controller uPD98502 User Manual

Page 376

CHAPTER 7 PCI CONTROLLER

376

Preliminary User’s Manual S15543EJ1V0UM

7.2.2 PCI to internal bus transaction

7.2.2.1 Window size

The PCI Controller supports a 2-MB address space as the access window from PCI-side to Internal bus-side in PCI

memory space. The base address for the window is written to Window Memory Base Address register in configuration

space by an external PCI-Host device in NIC mode. In Host-mode, the V

R

4120A has to write the base address to this

register.

The internal registers of the PCI Controller cannot be read/written through this window even when it includes the

address area of the PCI Controller. The base address for registers, which is written in Register Memory Base Address

register in configuration space, has to be used in order to read/write to the internal registers of the PCI Controller.

When the issued burst transfer goes over the boundary of the address space, the PCI Controller issues

“disconnect” at the boundary.

7.2.2.2 Access type

(1) PCI target

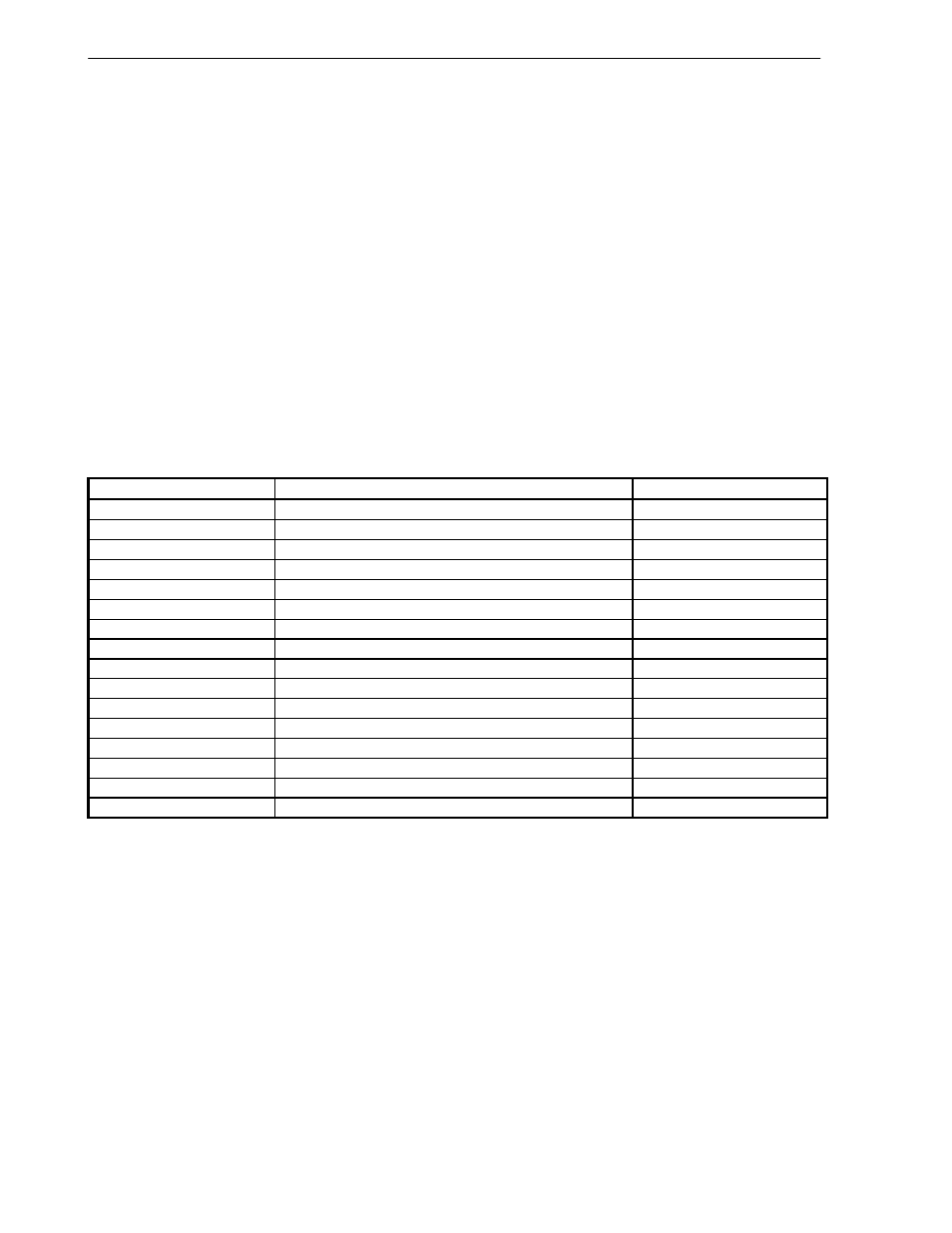

The acceptable PCI commands for the PCI Controller are as follows.

C/BE#[3:0]

PCI commands

As PCI Target

0000

Interrupt Acknowledge

Ignored

0001

Special Cycle

Ignored

0010

I/O Read

Ignored

0011

I/O Write

Ignored

0100

Reserved

-

0101

Reserved

-

0110

Memory Read

Accepted

0111

Memory Write

Accepted

1000

Reserved

-

1001

Reserved

-

1010

Configuration Read

Accepted

1011

Configuration Write

Accepted

1100

Memory Read Multiple

Accepted

1101

Dual Address Cycle

Ignored

1110

Memory Read Line

Accepted

1111

Memory Write and Invalidate

Accepted

(2) Internal bus

When ICMDS bit in P_BCNT register is ‘0’, the PCI Controller uses I/O command on Internal bus. In the case that

ICMDS bit is ‘1’, the PCI Controller uses memory command on Internal bus.