9 sdptr (sdram precharge timing register), 10 sdrmr (sdram refresh mode register) – NEC Network Controller uPD98502 User Manual

Page 211

CHAPTER 3 SYSTEM CONTROLLER

Preliminary User’s Manual S15543EJ1V0UM

211

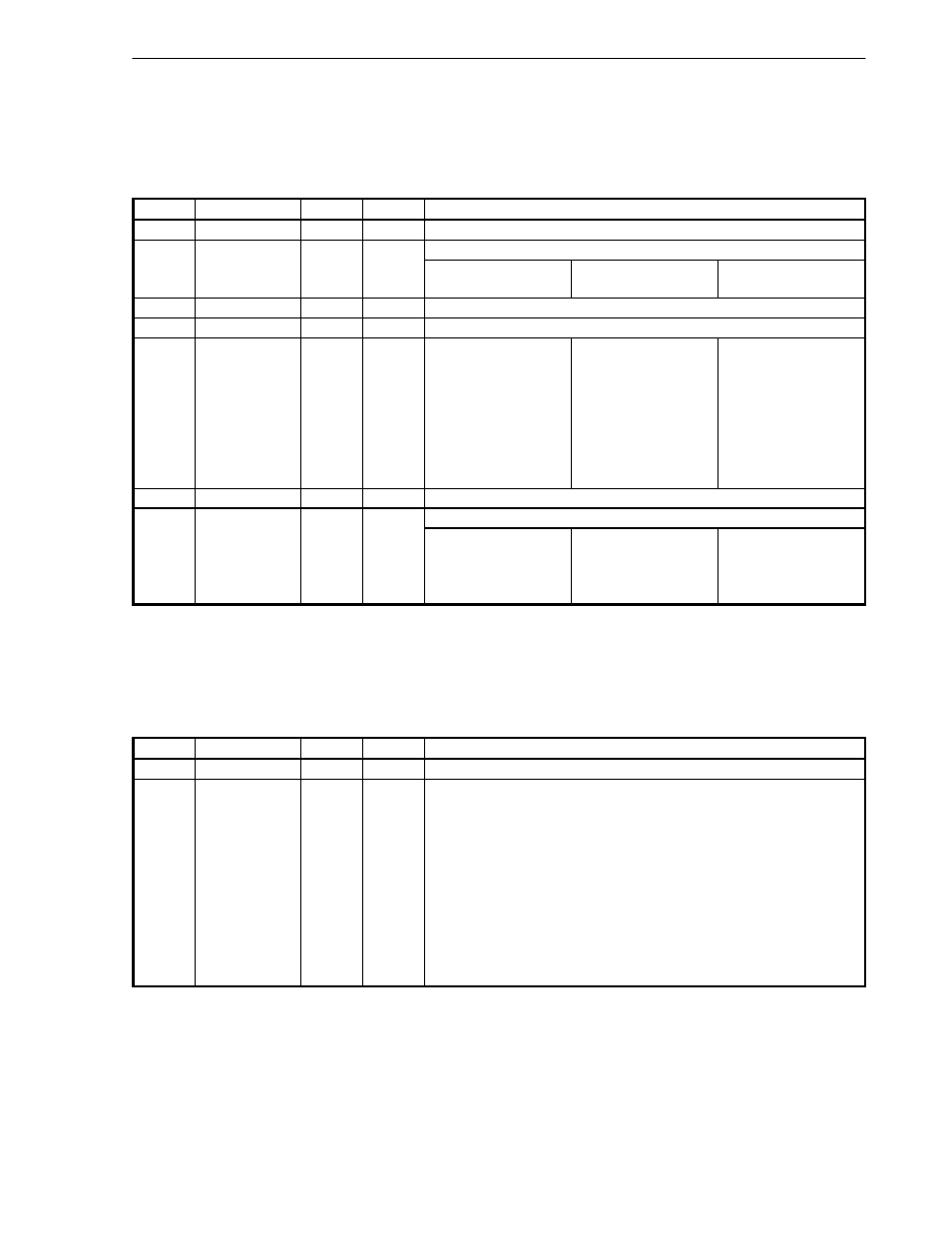

3.4.9 SDPTR (SDRAM Precharge Timing Register)

The SDRAM precharge timing register “SDPTR” is a read-write and 32-bit word-aligned register. SDPTR is used to

set the precharge timing for the SDRAM controller. SDPTR is initialized to 142H at reset and contains the following

fields:

Bits

Field

R/W

Default

Description

31:9

Reserved

R/W

0

Hardwired to 0.

Input data -> precharge command timing (t

DPL

):

8

DPL

R/W

1

0 = 1 clock

1 = 2 clocks (default)

66 MHz: 15.2 ns

66 MHz: 30.3 ns

100 MHz: 10 ns

100 MHz: 20 ns

7

Reserved

R/W

0

Hardwired to 0.

6:4

APT

R/W

100

Active command -> precharge command timing (t

RAS

):

000 = 4 clocks

001 = 5 clocks

010 = 6 clocks

011 = 7 clocks

100 = 8 clocks (default)

101 = reserved

110 = reserved

111 = reserved

66 MHz: 60.6 ns

66 MHz: 75.7 ns

66 MHz: 90.9 ns

66 MHz: 106.0 ns

66 MHz: 121.2 ns

100 MHz: 40 ns

100 MHz: 50 ns

100 MHz: 60 ns

100 MHz: 70 ns

100 MHz: 80 ns

3:2

Reserved

R/W

0

Hardwired to 0.

Precharge command -> active command timing (t

RP

):

1:0

PAT

R/W

10

00 = 2 clocks

01 = 3 clocks

10 = 4 clocks (default)

11 = reserved

66 MHz: 30.3 ns

66 MHz: 45.5 ns

66 MHz: 60.6 ns

100 MHz: 20 ns

100 MHz: 30 ns

100 MHz: 40 ns

Remark

Don’t set the reserved value to each field in this register.

3.4.10 SDRMR (SDRAM Refresh Mode Register)

The SDRAM refresh mode register “SDRMR” is a read-write and 32-bit word-aligned register. SDRMR is used to

initialize the SDRAM refresh controller. SDRMR is initialized to 200H at reset and contains the following fields:

Bits

Field

R/W

Default

Description

31:16

Reserved

R/W

0

Hardwired to 0.

15:0

RCSET

R/W

0200H

Reload value for SDRAM refresh timer counter.

This value, in system clock ticks, is automatically reloaded into the refresh

timer counter after the counter reached zero. The refresh timer counter

counts down from this value. Thus, time of the count cycle corresponds to 1

plus this filed value. The default value (200H = 512) is the refresh rate for an

SDRAM chip that requires 4096 refresh cycles every 32 ms (ex. one refresh

every 7.8125

µs) for system clock running at 66 MHz. This is very

conservative but it allows for successful boot, after which the reload value

can be increased. RCSET [7:0] is hardwired to 0, thus the timer value less

than 100H cannot be set this field. If such value is set into this field, the

default value “200H” is automatically loaded.