NEC Network Controller uPD98502 User Manual

Page 404

CHAPTER 7 PCI CONTROLLER

404

Preliminary User’s Manual S15543EJ1V0UM

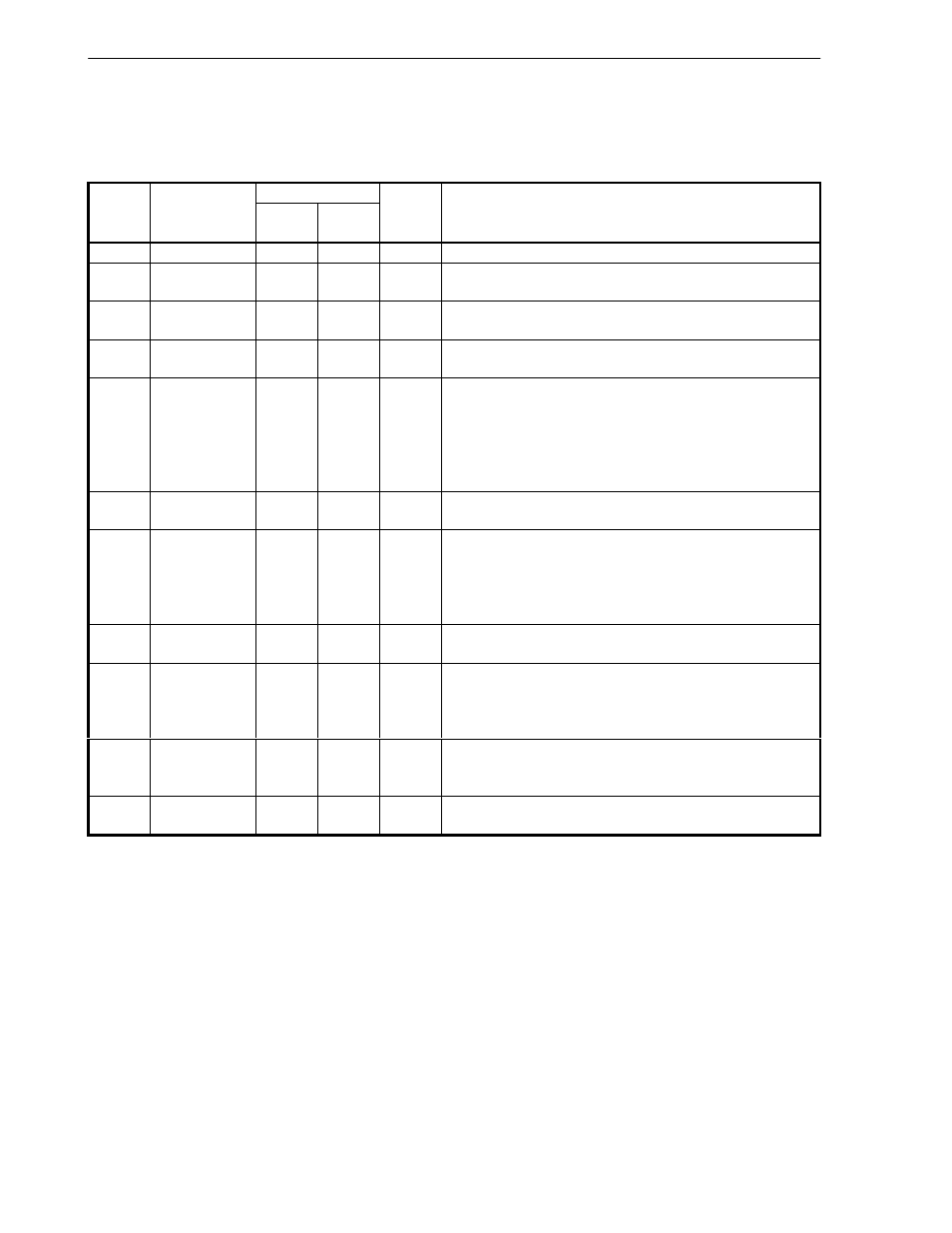

7.5.19.4 Command register

This register provides coarse control over a device’s ability to generate and respond to PCI cycles. This register is

valid in Host-mode. The V

R

4120A should set the register.

R/W

Bits

Field

Internal

bus

PCI

Default

Description

15:10

Reserved

R

R

0

Hardwired to ‘0’s.

9

Fast Back-to-

Back Enable

R

R

0

Hardwired to a ‘0’, because the PCI Controller cannot generate

fast back-to-back transaction.

8

System Error

Enable

R/W

R/W

0

This bit is an enable bit for the SERR_B driver. ‘1’ enables the

SERR_B driver.

7

Wait Cycle

Enable

R

R

0

Hardwired to a ‘0’, because the PCI Controller does not use

address/data stepping as PCI-device.

6

Parity Error

Response

R/W

R/W

0

This bit controls the PCI Controller’s response to parity errors.

When the bit is set to a ‘0’, the PCI Controller must take its normal

action if a parity error is detected. When the bit is set to a ‘1’, the

PCI Controller sets its Detected Parity Error status bit (bit15 in the

Status register) if an error is detected, but does not assert

PERR_B and continues normal operation.

5

VGA Palette

Snoop Enable

R

R

0

Hardwired to a ‘0’, because the PCI Controller does not have

VGA function.

4

Memory Write

and Invalidate

Enable

R/W

R/W

0

This is an enable bit for using the Memory Write and Invalidate

command. When this bit is set to a ‘1’, the PCI Controller can

generate the Memory Write and Invalidate command. When it is a

‘0’, Memory Write is used and Memory Write and Invalidate

command is not issued.

3

Special Cycle

Recognition

R

R

0

Hardwired to a ‘0’, because the PCI Controller dose not respond

to Special Cycle operations.

2

Bus Master

Enable

R/W

R/W

0

Controls The PCI Controller’s ability to act as a master on the PCI

bus. ‘0’ disables the PCI Controller from generating PCI

accesses. ‘1’ allows the PCI Controller to behave as a bus

master.

1

Memory Access

Enable

R/W

R/W

0

Controls a device’s response to Memory Space accesses. ‘0’

disables The PCI Controller’s response. ‘1’ allows the PCI

Controller to respond to Memory space accesses.

0

I/O Access

Enable

R

R

0

Hardwired to ‘0’, because the PCI Controller does not issue the

I/O space.