NEC Network Controller uPD98502 User Manual

Page 184

CHAPTER 2 V

R

4120A

184

Preliminary User’s Manual S15543EJ1V0UM

2.8.5.2 Masking interrupt signals

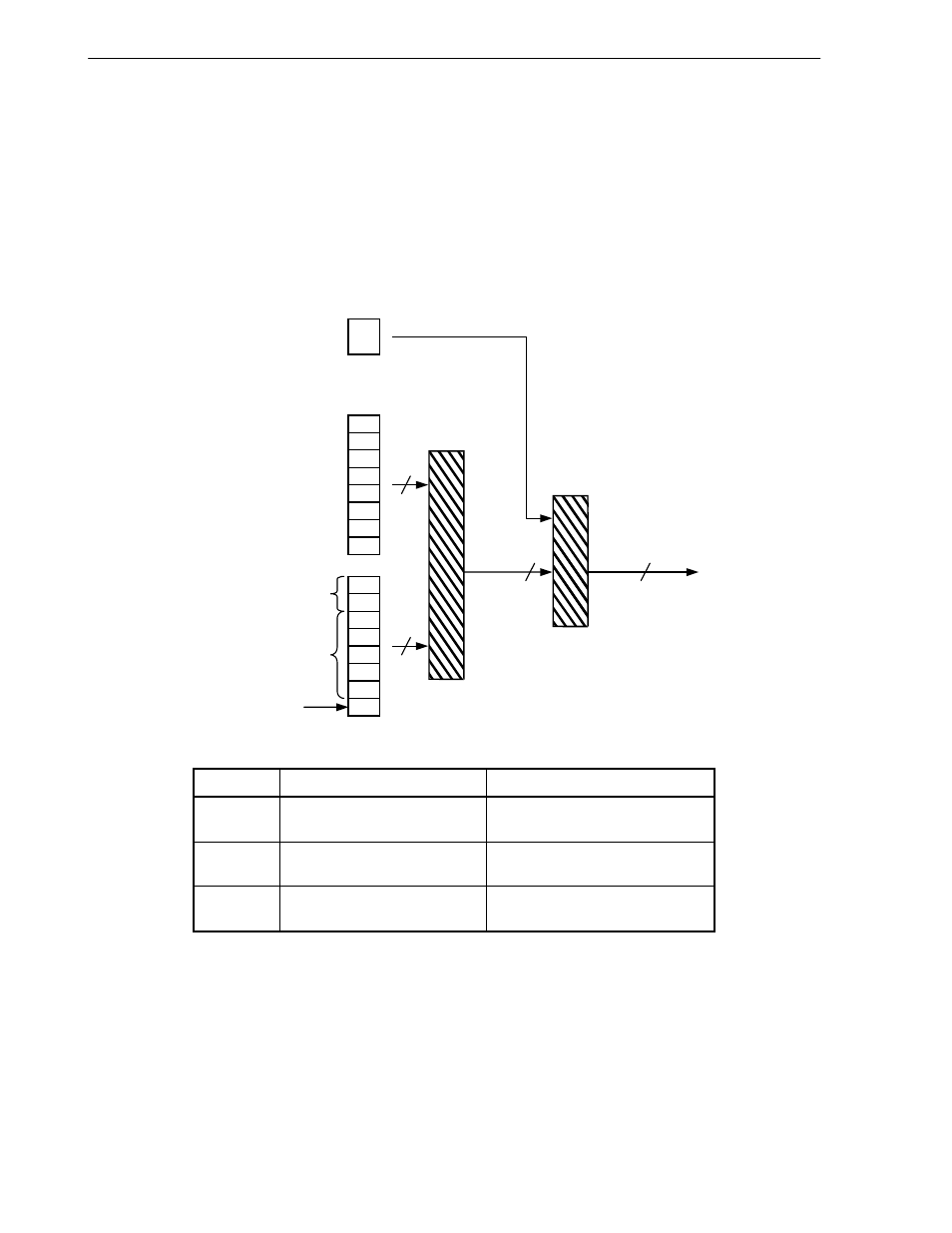

Figure 2-89 shows the masking of the CPU core interrupt signals.

Cause register bits 15 to 8 (IP7 to IP0) are AND-ORed with Status register interrupt mask bits 15 to 8 (IM7 to

IM0) to mask individual interrupts.

Status register bit 0 is a global Interrupt Enable (IE). It is ANDed with the output of the AND-OR logic shown

in Figure 2-89 to produce the CPU core interrupt signal. The EXL bit in the Status register also enables

these interrupts.

Figure 2-89. Masking of Interrupt Request Signals

Timer interrupt

IM0

IE

Software interrutpts

generated in CPU core

Status register

SR0

IM1

IM2

IM3

IM4

IM5

IM6

IM7

IP0

IP1

IP2

IP3

IP4

IP5

IP6

IP7

Ordinary

interrupts

Status register

SR (15:8)

Cause register

(15:8)

8

AND-OR block

AND block

1

1

CPU core interrupt

8

8

9

10

11

12

13

14

15

8

9

10

11

12

13

14

15

Bit

Function

Setting

IE

Whole interrupts enable

1 : Enable

0 : Disable

IM(7:0)

Interrupt mask

Each bit

1 : Enable

0 : Disable

IP(7:0)

Interrupt request

Each bit

1 : Pending

0 : Not pending