16 p_ppcr (pci power control register), 17 p_swrr (software reset register) – NEC Network Controller uPD98502 User Manual

Page 400

CHAPTER 7 PCI CONTROLLER

400

Preliminary User’s Manual S15543EJ1V0UM

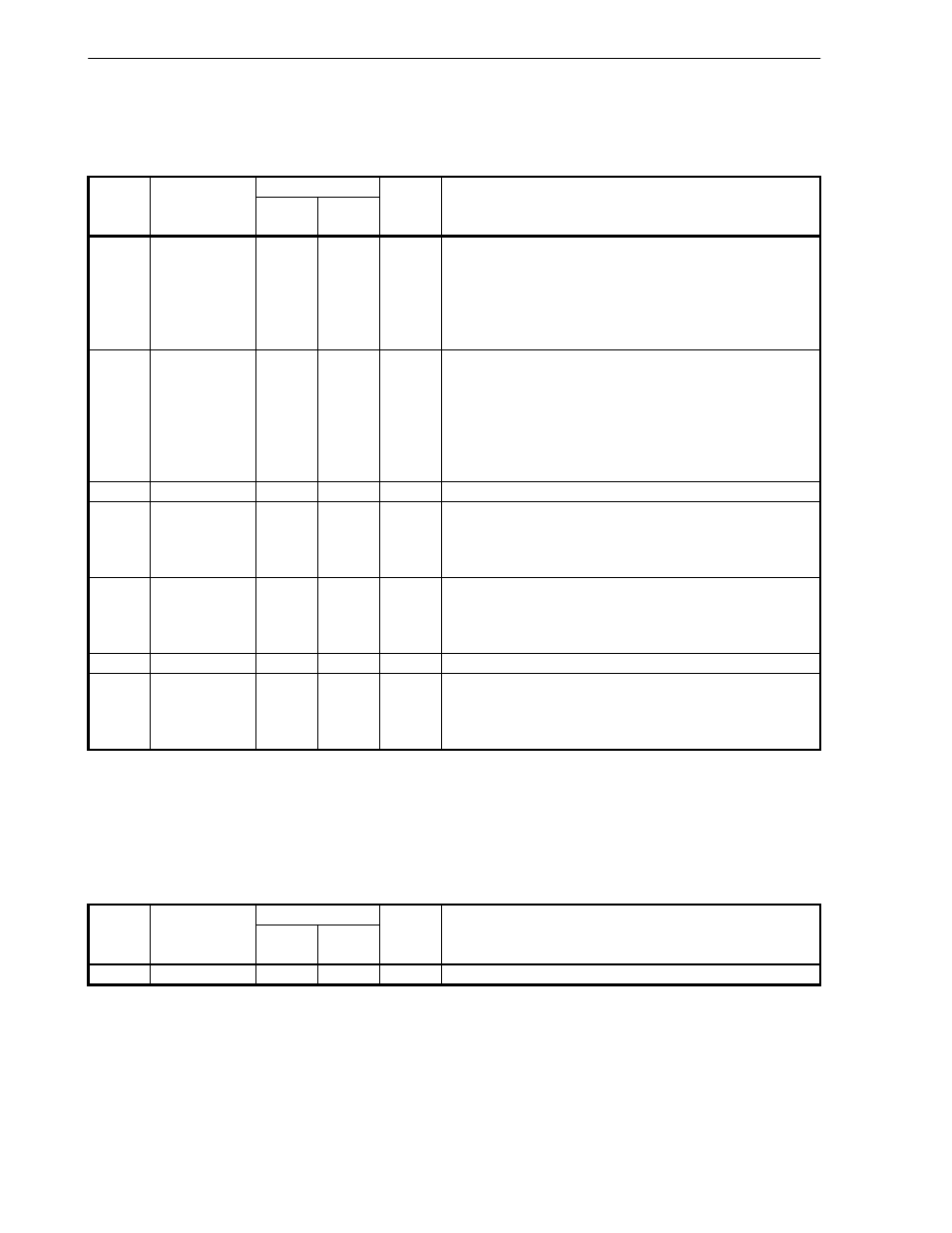

7.5.16 P_PPCR (PCI Power Control Register)

This register is used to control the power state for PPMI.

See 7.6 Information for Software for further details.

R/W

Bits

Field

Internal

bus

PCI

Default

Description

31

PMRDY

R/W

R

0

Power Management Ready.

‘1’ indicates that the transition of power state has been done.

When PCI-Host writes to PowerState field of PMCSR register in

Configuration Space, this bit is reset to ‘0’. the V

R

4120A should

be set ‘1’ to this bit after the transition of power state has been

done.

30

PMERQ

W

-

0

PME# issue.

This bit is only writeable from Internal bus-side.

The PCI Controller asserts PME# signal when ‘1’ is written to this

bit.

If PCI-Host want to clear PME# asserting, it should write ‘1’ to

PME_Status bit in PMCSR register, or disable PME_En bit in

PMCSR register. See 7.6 for further details.

29:4

Reserved

-

-

0

Hardwired to ‘0’s.

3

PMRQ0

R/W

R

0

The transition to D0 power state issued.

‘1’ indicates that PCI-Host issues the transition to D0 state.

The V

R

4120A should write ‘1’ to this bit in order to clear after the

recognition that this bit is set.

2

PMRQ1

R/W

R

0

The transition to D1 power state issued.

‘1’ indicates that PCI-Host issues the transition to D1 state.

The V

R

4120A should write ‘1’ to this bit in order to clear after the

recognition that this bit is set.

1

Reserved

-

-

0

Hardwired to a ‘0’.

0

PMRQ3

R/W

R

0

The transition to D3 power state issued.

‘1’ indicates that PCI-Host issues the transition to D3 state.

The V

R

4120A should write ‘1’ to this bit in order to clear after the

recognition that this bit is set.

7.5.17 P_SWRR (Software Reset Register)

This register is used for Software Reset and can be written only from PCI-side. Writing any value to this register

causes the Software Reset. When this register is written, the SRREQ bit in P_IGSR register will be set and an internal

interrupt will be asserted to the V

R

4120A. The V

R

4120A is responsible to execute reset-operations (for example,

asserting warm-reset to all blocks).

R/W

Bits

Field

Internal

bus

PCI

Default

Description

31:0

SWRS

-

W

-

This register is write-only.