6 s_nsr (nmi status register) – NEC Network Controller uPD98502 User Manual

Page 194

CHAPTER 3 SYSTEM CONTROLLER

194

Preliminary User’s Manual S15543EJ1V0UM

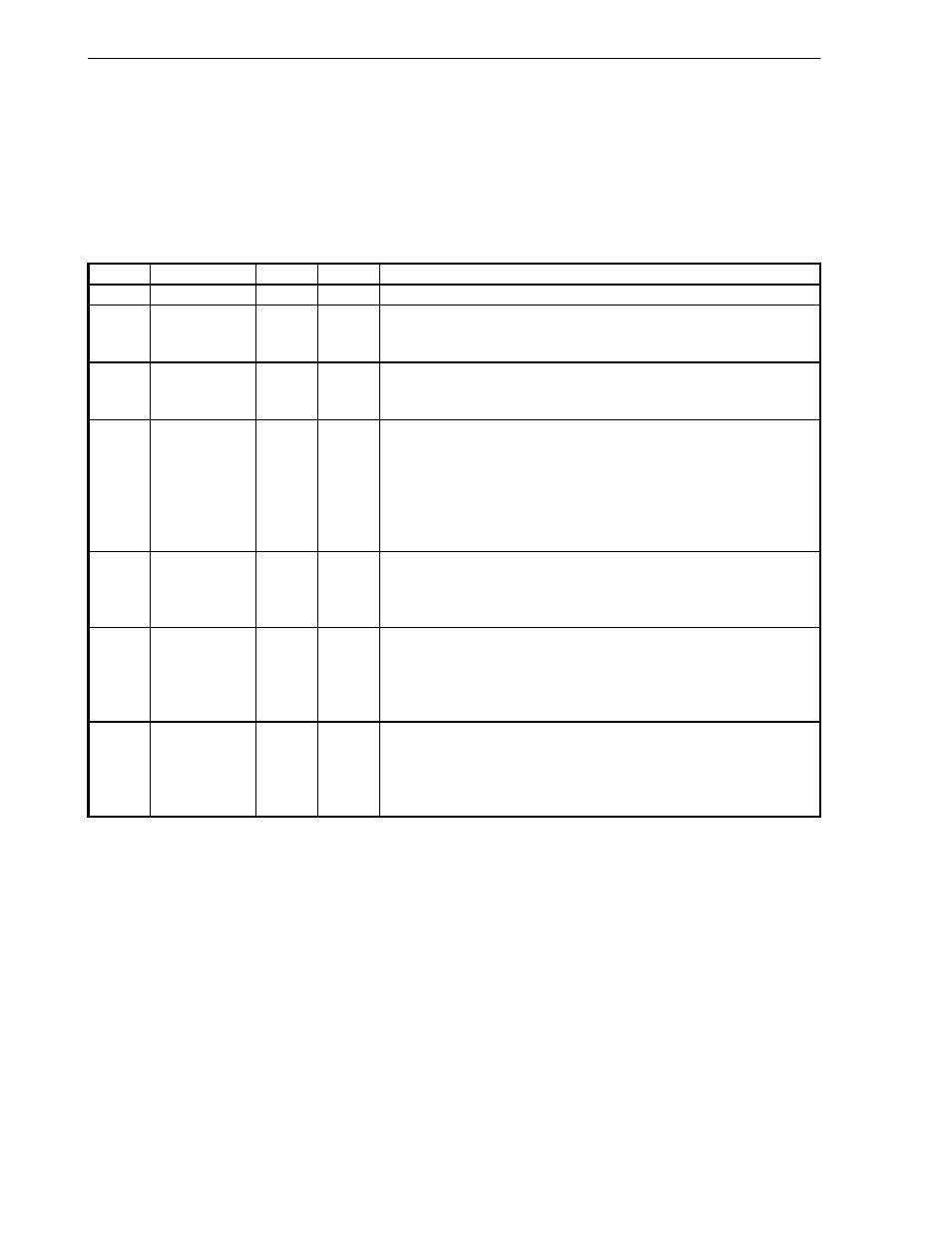

3.2.6 S_NSR (NMI Status Register)

The interrupt status register “S_NSR” is a read-clear and 32-bit word-aligned register. S_NSR indicates the non-

maskable interruption “NMI” status from SysAD/IBUS interfaces, external NMI, memory interface and so on. If

corresponding bit in S_NER (NMI Enable Register) is set and the NMI is enabled, system controller interrupts to

V

R

4120A using non-maskable interrupt signal. The bit in S_NSR is reset after being read by the V

R

4120A. When the

same type of incident occurs before the bit has been read, the bit will be set again. S_NSR is initialized to 0 at reset

and contains the following fields:

Bits

Field

R/W

Default

Description

31:6

Reserved

RC

0

Hardwired to 0.

5

IRERR

RC

0

Illegal internal register access error:

0 = no such access.

1 = illegal internal register access, ex burst access has been performed.

4

EXTNMI

RC

0

External NMI:

0 = external NMI is not asserted.

1 = external NMI is asserted.

3

MAERR

RC

0

Memory address error:

Memory address error includes the memory access to the illegal memory

space (RFU space and out range of the SDRAM/ROM space) and the illegal

memory access (byte or half-word ROM access or burst write access to the

ROM).

0 = no such error.

1 = an address range error occurred during the memory access.

2

ITERR

RC

0

IBUS timeout error:

IBUS timeout error is occurred when the IBUS is stalled.

0 = no such error.

1 = IBUS timeout error.

1

IBERR

RC

0

IBUS bus error:

IBUS bus error is occurred when V

R

4120A accesses to the RFU area in the

IBUS target address space (see 1.9 Memory Map section).

0 = no such error.

1 = a bus error occurred during the IBUS master access.

0

CBERR

RC

0

CPU (V

R

4120A) bus error:

V

R

4120A bus error includes the illegal bus command, illegal data align, illegal

bust size, and illegal access to the RFU area in register space.

0 = no such error.

1 = V

R

4120A bus error.

Remark

To clear this register, the V

R

4120A must read the byte contained the CBERR register.