NEC Network Controller uPD98502 User Manual

Page 160

CHAPTER 2 V

R

4120A

160

Preliminary User’s Manual S15543EJ1V0UM

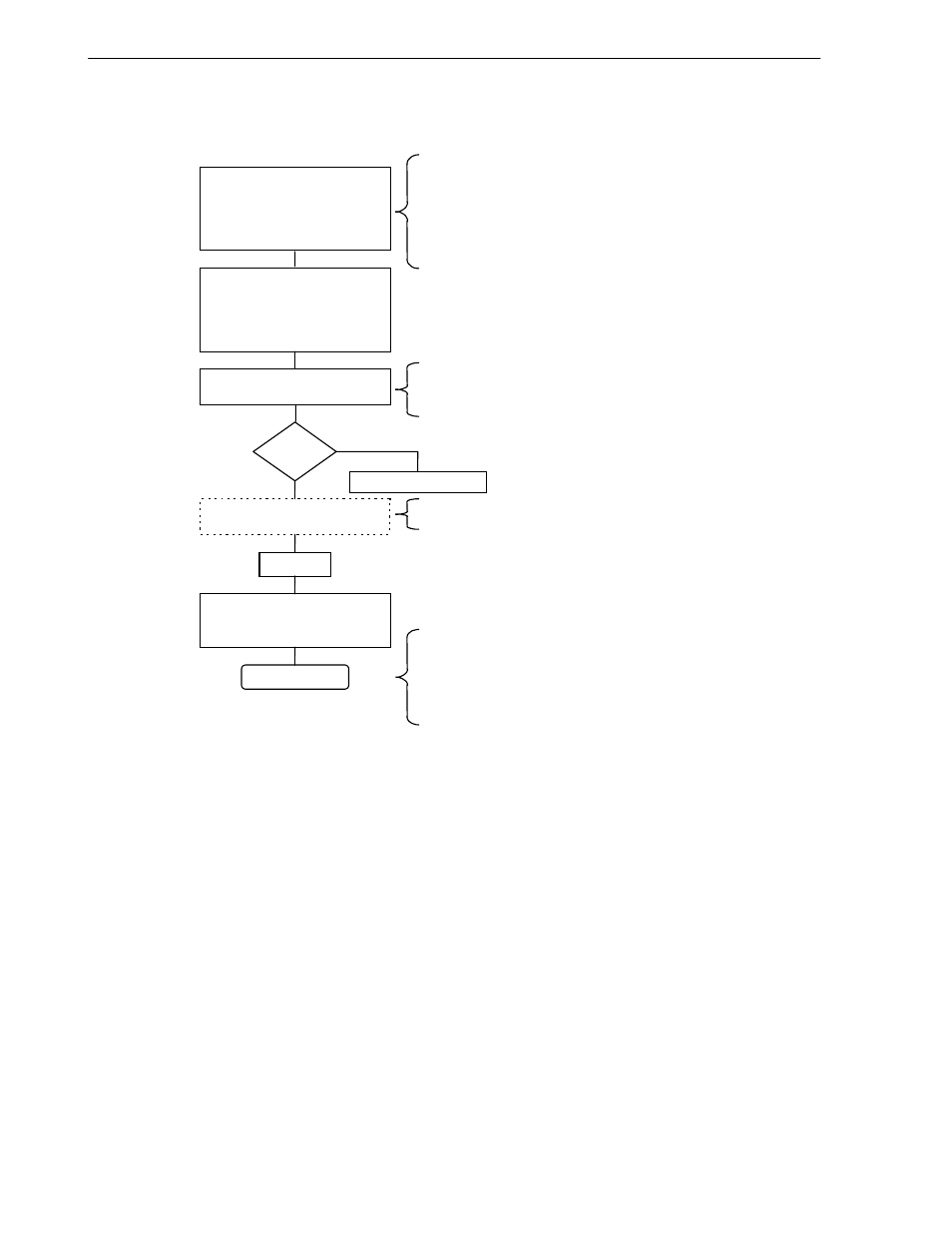

Figure 2-61. Common Exception Handling (2/2)

(b) Servicing Common Exceptions (Software)

The processor is reset.

(In Kernel mode, interrupts are enabled.)

• After EXL = 0 is set, all exceptions are enabled (although the

Interrupt exception can be masked by the IE and IM bits, and the

Cache Error exception can be masked by the DE bit.)

• The occurrence of TLB Refill, TLB Invalid, and TLB Modified

exceptions is disabled by using an unmapped space.

• The occurrence of the Watch and Interrupt exceptions is

disabled by setting EXL = 1.

• Other exceptions are avoided in the OS programs.

• However, the Cold Reset, Soft Reset, and NMI exceptions are

enabled.

Execute MFC0 instruction

(Status bit setting)

KSU bit

← 00

EXL bit

← 0

IE bit

← 1

Execute MFC0 instruction

X/Context register

EPC register

Status register

Cause register

ERET

Servicing by each exception routine

Check the Cause register, and jump

to each routine

TS bit = 0?

Yes

No

• The register files are saved.

EXL = 1

Execute MTC0 instruction

EPC register

Status register

• The execution of the ERET instruction is disabled in the

delay slots for the other jump instructions.

• The processor does not execute an instruction in the branch

delay slot for the ERET instruction.

• PC ← EPC, EXL ← 0