4 power state transition – NEC Network Controller uPD98502 User Manual

Page 384

CHAPTER 7 PCI CONTROLLER

384

Preliminary User’s Manual S15543EJ1V0UM

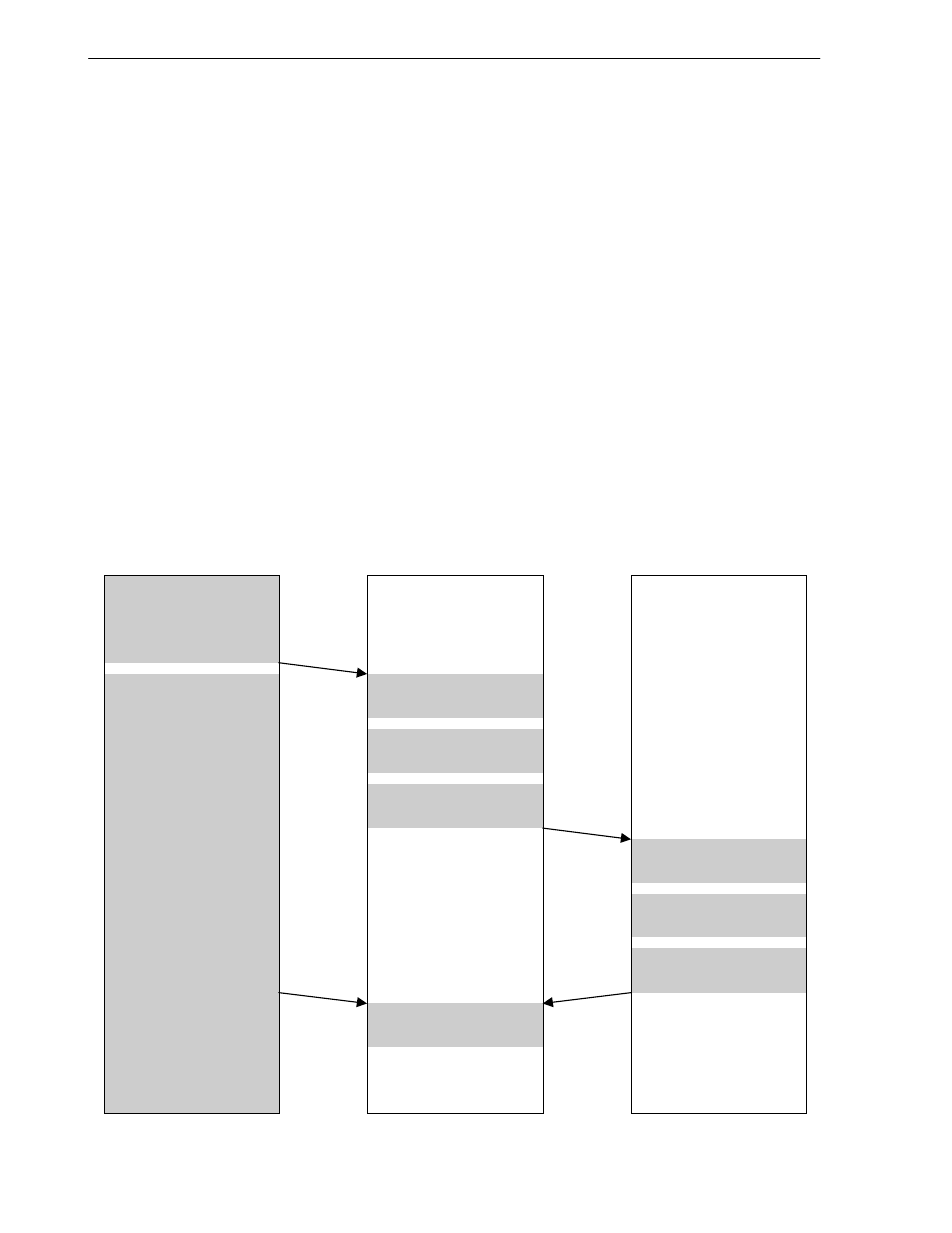

7.3.4 Power state transition

7.3.4.1 Transition by issue from PCI-Host

An example of the transition sequence is as follows:

1.

When PCI-Host wants to change the power state of the chip, it writes the state code to Power State field in

PMCSR register.

2.

The PCI Controller resets PMRDY bit in P_PPCR register to a ‘0’.

3.

The PCI Controller sets PMRQX bit (PMRQ0, PMRQ1, and PMRQ3) in P_PPCR register, and issues an

interrupt to the V

R

4120A (if not masked).

4.

The V

R

4120A clears the interrupt by reading PGSR register and knows the transition of power state is issued.

5.

Then, the V

R

4120A knows which power state is issued by reading P_PPCR register.

6. The

V

R

4120A executes the operations for the system that the chip is used in, if needed.

7.

When the V

R

4120A is ready for the transition, the V

R

4120A writes a ‘1’ to PMRDY bit in P_PPCR register.

8.

An external PCI-Host device is able to know that the chip is ready by reading PMRDY bit. The PCI-Host

device does not need to wait the completion of the preparation of the chip. Therefore, power and clock may

be removed suddenly.

Figure 7-10. The Sequence of the Transition by Issues from PCI-Host

r e q u e s t t h e t r a n s it io n o f

t h e p o w e r s t a t e t o P C I

C ontroller by w riting to

P o w e r S t a te f ie ld in

P M C S R r e g is t e r

reset P M R D Y b it to '0'

in P P C R reg ister

set P M R Q X b it to '1'

in P P C R reg ister

rep o rt to th e in tern al

co n tro ller b y

In terru p t

read P G S R reg ister

an d clear In terru p t

o p eratio n fo r th e

tran sitio n o f th e

p o w er state

w rite '1 ' to P M R D Y b it

in P P C R re g is ter

set '1' to P M R D Y b it

in P P C R reg ister

ch an g e th e P C I-b u s

p o w er state

write

Interrupt

write

check

P M R D Y

bit or not

depends

on P C I-

H ost

(optional)

P C I-H ost

P C I

C ontroller

Internal

C ontroller