Dmacc, Doubleword multiply and accumulate (1/3) – NEC Network Controller uPD98502 User Manual

Page 477

APPENDIX A MIPS III INSTRUCTION SET DETAILS

Preliminary User’s Manual S15543EJ1V0UM

477

DMACC

Doubleword Multiply and Accumulate (1/3)

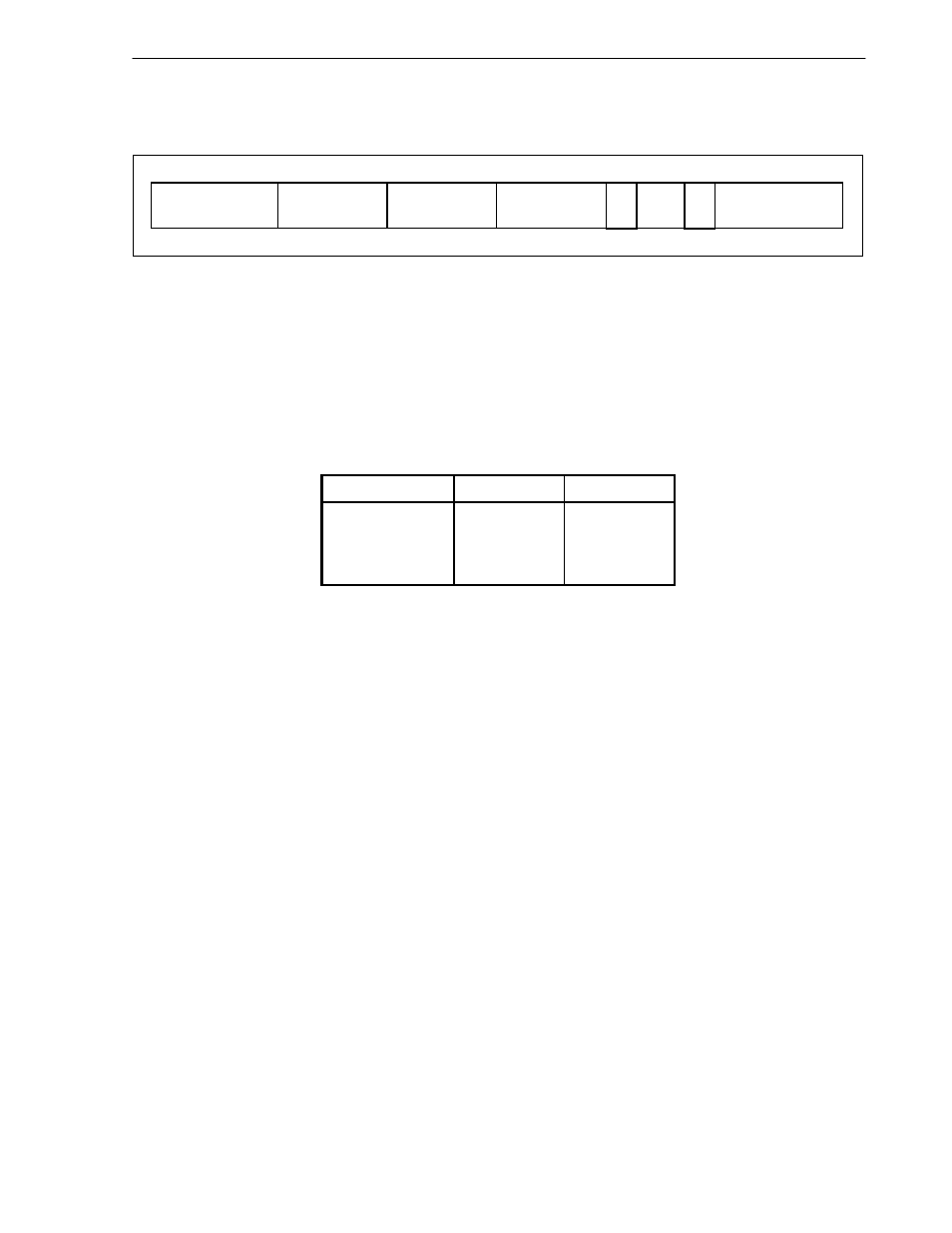

DMACC

rs

SPECIAL

0 0 0 0 0 0

rt

1

31

26 25

21 20

16 15

0

6

5

5

DMACC

1 0 1 0 0 1

6

5

6

rd

sat

us

0 0 0

1

5

3

11 10

9

7

Format:

DMACC rd, rs, rt

DMACCU rd, rs, rt

DMACCS rd, rs, rt

DMACCUS rd, rs, rt

Description:

DMACC instruction differs mnemonics by each setting of op codes sat, hi and us as follows.

Mnemonic

sat

us

DMACC

DMACCU

DMACCS

DMACCUS

0

0

1

1

0

1

0

1

The number of significant bits in the operands of the DMACC instruction differ depending on whether saturation

processing is executed (sat = 1) or not executed (sat = 0).

• When saturation processing is executed (sat = 1): DMACCS, DMACCUS instructions

The contents of general register

rs is multiplied by the contents of general register rt. If both operands are set

as "us = 1" (DMACCUS instruction), the contents are handled as 16 bit unsigned data. If they are set as "us =

0" (DMACCS instruction), the contents are handled as 16 bit signed integers. Sign/zero expansion by software

is required for any bits exceeding 16 bits in the operands.

The product of this multiply operation is added to the value in the LO special register. If us = 1, this add

operation handles the values being added as 32 bit unsigned data. If us = 0, the values are handled as 32 bit

signed integers. Sign/zero expansion by software is required for any bits exceeding 32 bits in the LO special

register.

After saturation processing to 32 bits has been performed (see the table below), the sum from this add

operation is loaded to the LO special register. When hi = 1, data that is the same as the data loaded to the HI

special register is also loaded to the rd general register. When hi = 0, data that is the same as the data loaded

to the LO special register is also loaded to the rd general register. Overflow exceptions do not occur.