11 sdrcr (sdram refresh timer count register), 12 mbcr (memory bus control register) – NEC Network Controller uPD98502 User Manual

Page 212

CHAPTER 3 SYSTEM CONTROLLER

212

Preliminary User’s Manual S15543EJ1V0UM

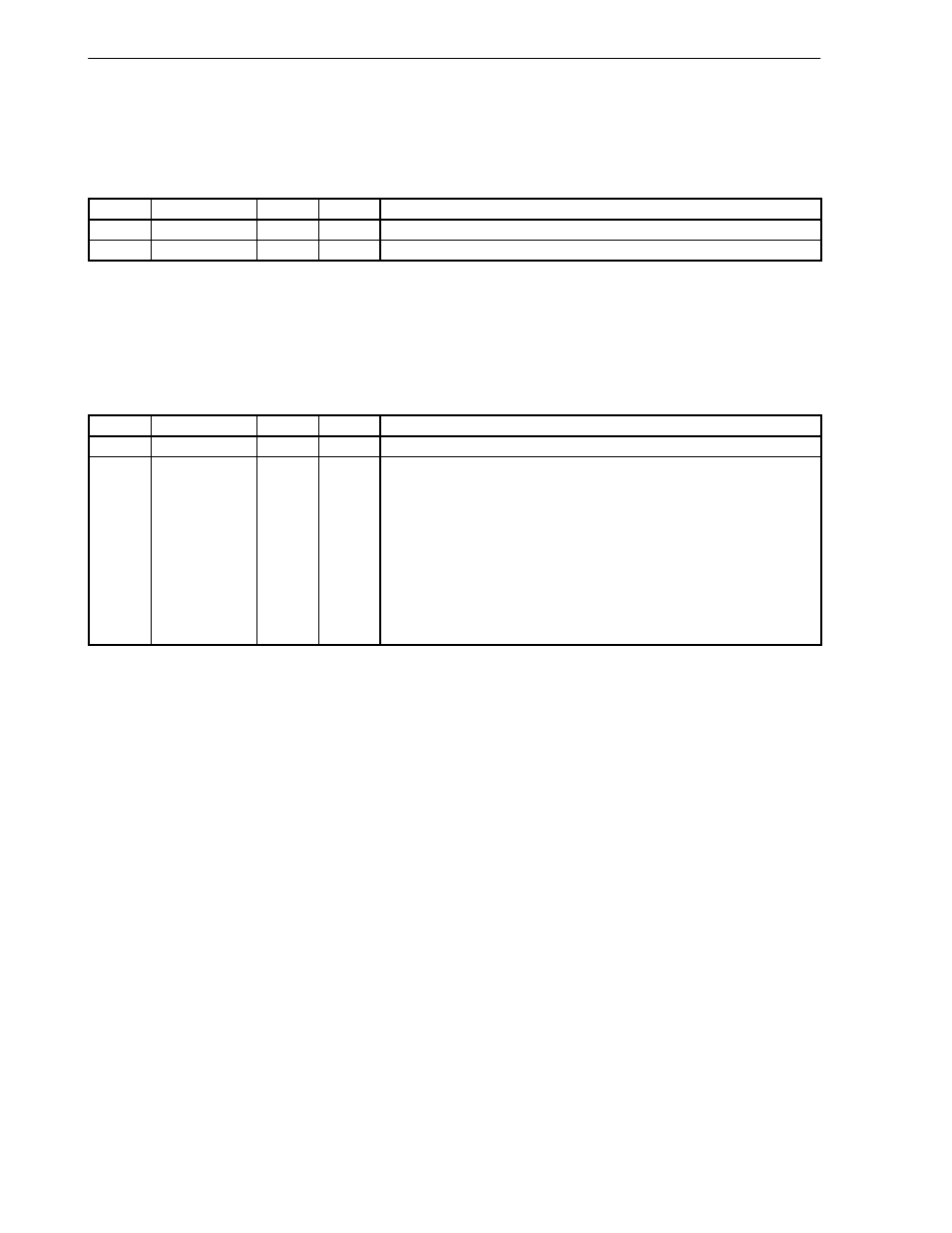

3.4.11 SDRCR (SDRAM Refresh Timer Count Register)

The SDRAM refresh timer count register “SDRCR” is a read-only and 32-bit word-aligned register. SDRCR is a 16-

bit timer that causes an SDRAM refresh when it expires. The SDRAM refresh controller automatically reloads this

free-running timer. SDRCR is initialized to 200H at reset and contains the following fields:

Bits

Field

R/W

Default

Description

31:16

Reserved

R

0

Hardwired to 0.

15:0

RCC

R

0200H

This field indicates the current value of SDRAM refresh timer.

3.4.12 MBCR (Memory Bus Control Register)

The memory bus control register “MBCR” is a read-write and 32-bit word-aligned register. MBCR is used to select

priority for either V

R

4120A or IBUS to access memory. The V

R

4120A can assign higher priority to CPU request for

memory than IBUS request or assign equal priority to V

R

4120A and IBUS request for memory. MBCR is initialized to 0

at reset and contains the following fields:

Bits

Field

R/W

Default

Description

31:1

Reserved

R/W

0

Hardwired to 0.

0

BPR

R/W

0

Priority for memory access:

0: SysAD (CPU) > Refresh > IBUS (default)

The memory arbiter allows one CPU memory transaction or refresh operation

even through the current memory access from IBUS is not yet completed.

CPU will be allowed to perform its memory access when the current word

count of burst access from IBUS reaches each 16 words or 32 words.

Refresh operation is also allowed to interrupt IBUS access.

1: SysAD (CPU) = Refresh = IBUS

Three operations are served in order of occurrence. Yet CPU will be granted

to access memory when three requests occur simultaneously.