Bgezall – NEC Network Controller uPD98502 User Manual

Page 452

APPENDIX A MIPS III INSTRUCTION SET DETAILS

452

Preliminary User’s Manual S15543EJ1V0UM

BGEZALL

Branch On Greater Than Or Equal To Zero And Link Likely

BGEZALL

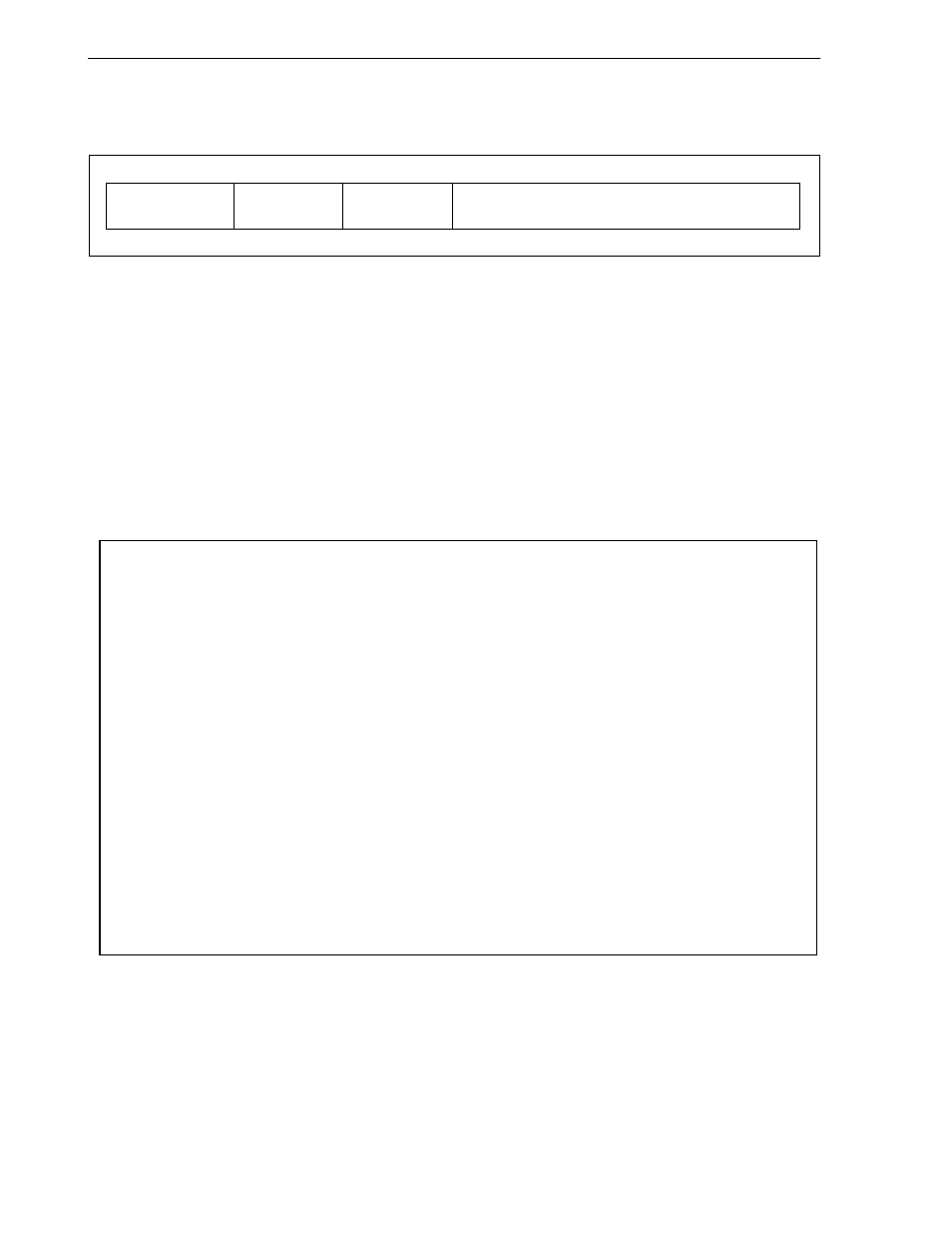

rs

REGIMM

0 0 0 0 0 1

BGEZALL

1 0 0 1 1

offset

31

26 25

21 20

16 15

0

6

5

5

16

Format:

BGEZALL rs, offset

Description:

A branch target address is computed from the sum of the address of the instruction in the delay slot and the 16-bit

offset, shifted left two bits and sign-extended. Unconditionally, the address of the instruction after the delay slot is

placed in the link register,

r31. If the contents of general register rs are zero or greater when compared to zero,

then the program branches to the target address, with a delay of one instruction. General register

r31 should not

be specified as general register

rs. If register r31 is specified, restarting may be impossible due to the destruction

of

rs contents caused by storing a link address. Even such instructions are executed, an exception does not result.

Operation:

32

T:

target

← (offset

15

)

14

|| offset || 0

2

condition

← (GPR [rs]

31

= 0)

GPR [31]

← PC + 8

T+1: if condition then

PC

← PC + target

else

NullifyCurrentInstruction

endif

64

T:

target

← (offset

15

)

46

|| offset || 0

2

condition

← (GPR [rs]

63

= 0)

GPR [31]

← PC + 8

T+1: if condition then

PC

← PC + target

else

NullifyCurrentInstruction

endif

Exceptions:

None