NEC Network Controller uPD98502 User Manual

Page 405

CHAPTER 7 PCI CONTROLLER

Preliminary User’s Manual S15543EJ1V0UM

405

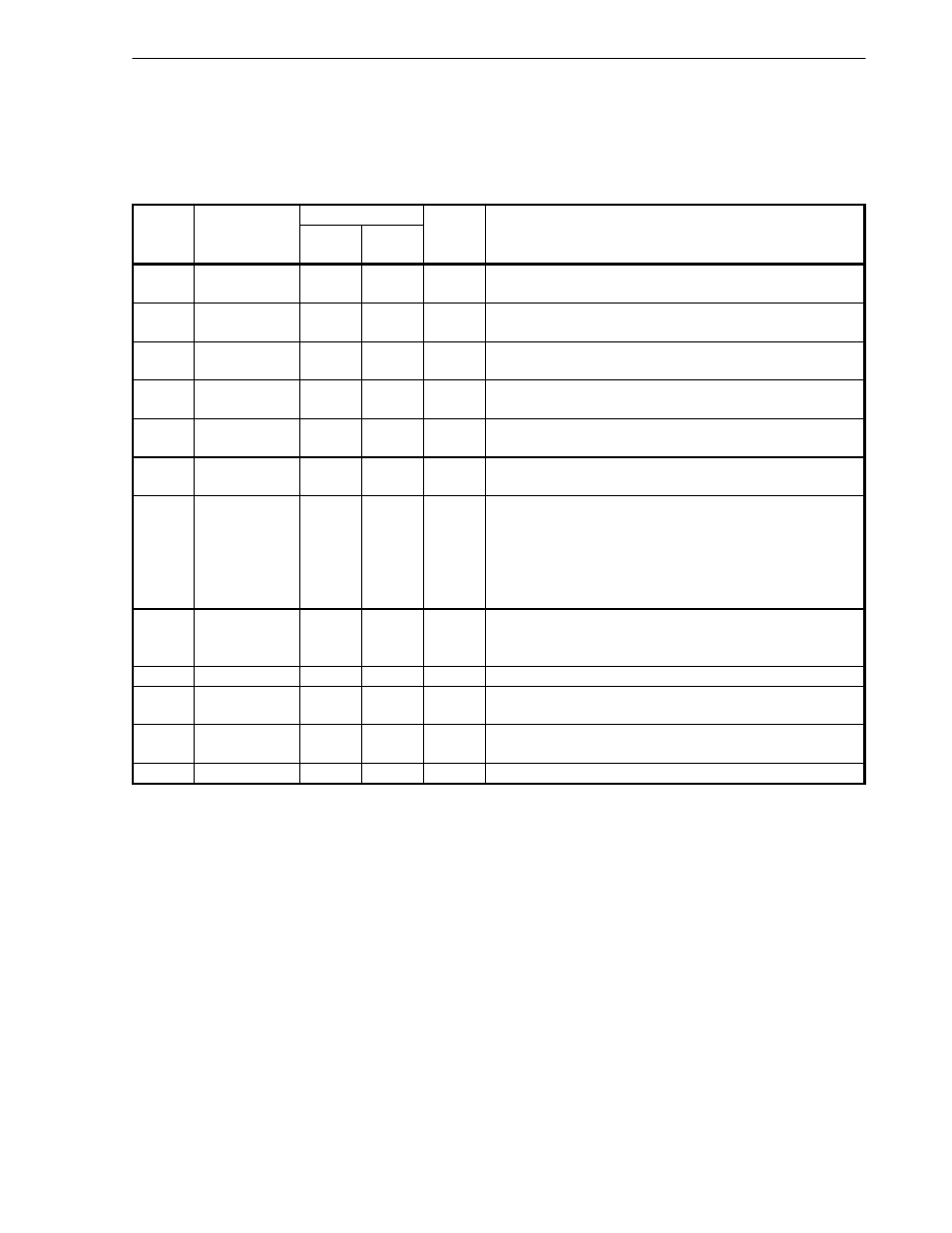

7.5.19.5 Status register

This register is used to show PCI bus related events status. These bits are set when events related to the status on

PCI bus and reset to ‘0’ by writing ‘1’.

In Host-mode, any bit in this register is not set even if corresponding events occur.

R/W

Bits

Field

Internal

bus

PCI

Default

Description

15

Detected Parity

Error

R/W

R/W

0

This bit is set to a ‘1’ when the PCI Controller detects a parity

error.

14

Signaled

System Error

R/W

R/W

0

This bit is set to a ‘1’ when the PCI Controller asserts SERR_B.

13

Received

Master Abort

R/W

R/W

0

This bit is set to a ‘1’ when the PCI Controller terminates its

transaction with Master-Abort as master device.

12

Received

Target Abort

R/W

R/W

0

This bit is set to a ‘1’ when the PCI Controller receives Target-

Abort and its transaction is terminated as master device.

11

Signaled Target

Abort

R/W

R/W

0

This bit is set to a ‘1’ when the PCI Controller terminates a

transaction with Target-Abort as target device.

10:9

DEVSEL_B

timing

R

R

01

Hardwired to ‘01’, because the PCI Controller asserts DEVSEL_B

at medium speed.

8

Master Data

Parity Error

R/W

R/W

0

This bit is set when three conditions as the follows are met:

(1) The bus agent asserted PERR_B itself (on a read) or

observed PERR_B asserted (on a write)

(2) The agent setting the bit acted as the bus master for the

operation in which the error occurred

(3) The Parity Error Response bit is set to a ‘1’

7

Fast Back-to-

Back Capable

R

R

0

Hardwired to a ‘0’, because the PCI Controller does not accept

fast back-to-back transactions when the transactions to the

different agents are required.

6

Reserved

R

R

0

Hardwired to a ‘0’.

5

66 MHz Enable

R

R

0

Hardwired to a ‘0’, because the PCI Controller can be used at

33 MHz only.

4

Capabilities List

R

R

1

Hardwired to a ‘1’, because the PCI Controller has the PPMI

function as New Capability.

3:0

Reserved

R

R

0

Hardwired to ‘0’s.