2 memory space – NEC Network Controller uPD98502 User Manual

Page 236

CHAPTER 4 ATM CELL PROCESSOR

236

Preliminary User’s Manual S15543EJ1V0UM

4.2 Memory Space

Although the RISC Core in the ATM Cell Processor is a 32-bit MPU, its physical memory space is 24-bit width.

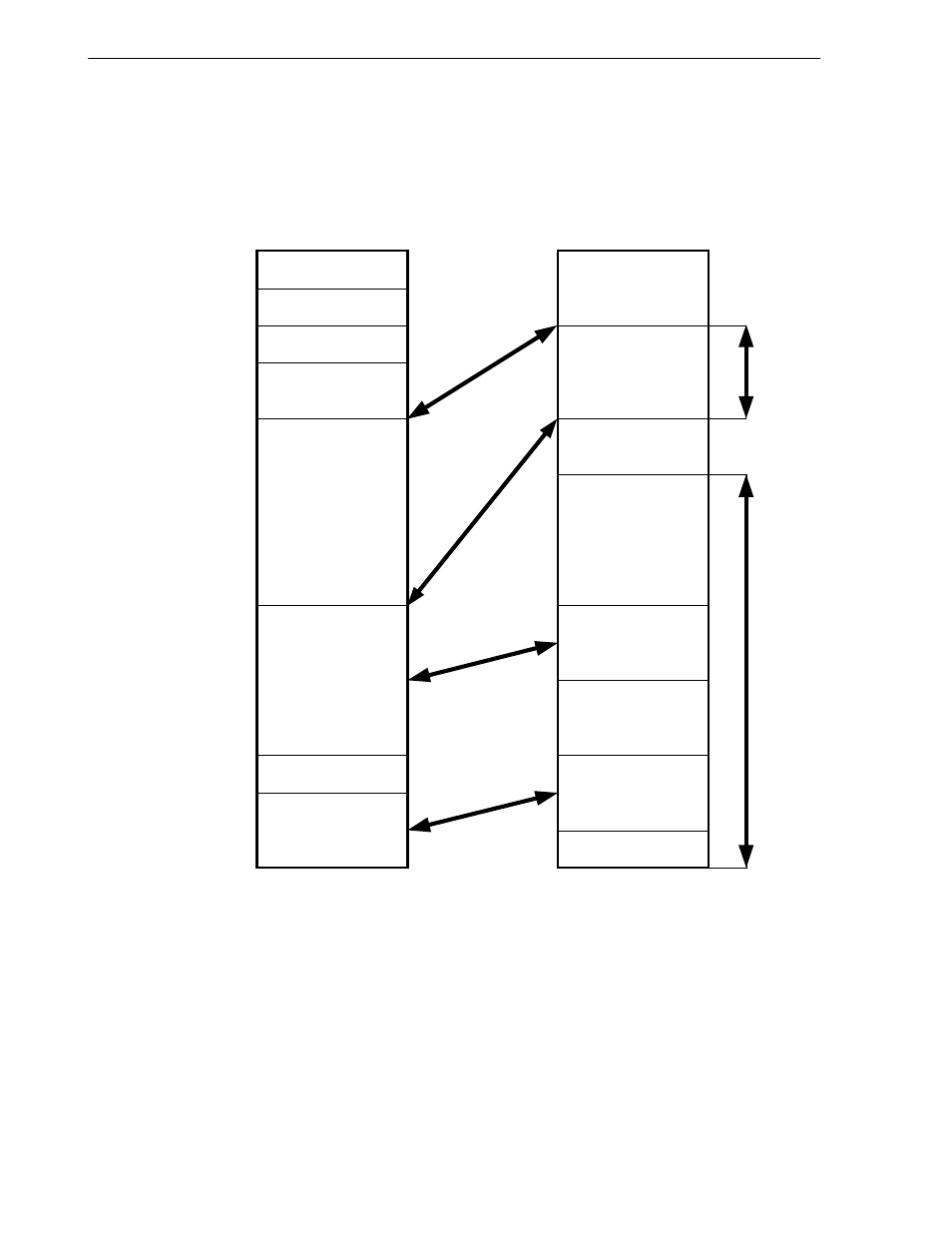

Figure 4-6. Memory Space from V

R

4120A and RISC Core

W o rk R A M &

R e giste r S p ace

In stru ctio n

spa ce

A _IB BA R :IBu s data B ase Ad dress R eg ister

A _IN B A R :Instru ction B ase A ddress R egister

S h a red

M em o ry

(4 M B m a x.)

4 0 _0 0 0 0 H +

(C o n te nt o f A _ IB B A R )

7 F _ F F F F H +

(C o n te nt o f A _ IB B A R )

(C o n te nt o f A _ IN B A R )

0 F _ F F F F H +

(C o n te nt o f A _ IN B A R )

S

DRA

M

S

p

a

c

e

64

K

In stru ctio n

spa ce

S h a red

M em o ry

(4 M B m a x.)

xx00 _ 00 0 0 H

xx0F_FFFFH

xx40 _ 00 0 0 H

xx80 _ 00 0 0 H

xx80_FFFFH

xxFF_FFFFH

xxFF_F000H

P e riph e ra l

xxFF_E 3 FFH

xxFF_ E 0 0 0H

In te rn a l D ata

R A M (1 K B )

R IS C C o re

M em o ry S pa ce

1001_FFFFH

1 00 1 _ 00 0 0H

V

R

4 12 0 A R IS C P roce sso r

M em o ry S pa ce

W o rk R A M &

R e giste r S p ace

The configuration is shown as Figure 4-6. It contains instruction space, shared memory space, work RAM, internal

memory space, and peripheral space.

V

R

4120A and RISC Core in the ATM Cell Processor share an external memory space. Shared memory will be

implemented by using SDRAM devices. The address in V

R

4120A memory space will be determined by S/W and

notified to RISC Core by setting A_IBBAR (IBUS data Base Address Register). Its capacity depends on the total

capacity of physical memory, but not exceeds 4 MB.