NEC Network Controller uPD98502 User Manual

Page 408

CHAPTER 7 PCI CONTROLLER

408

Preliminary User’s Manual S15543EJ1V0UM

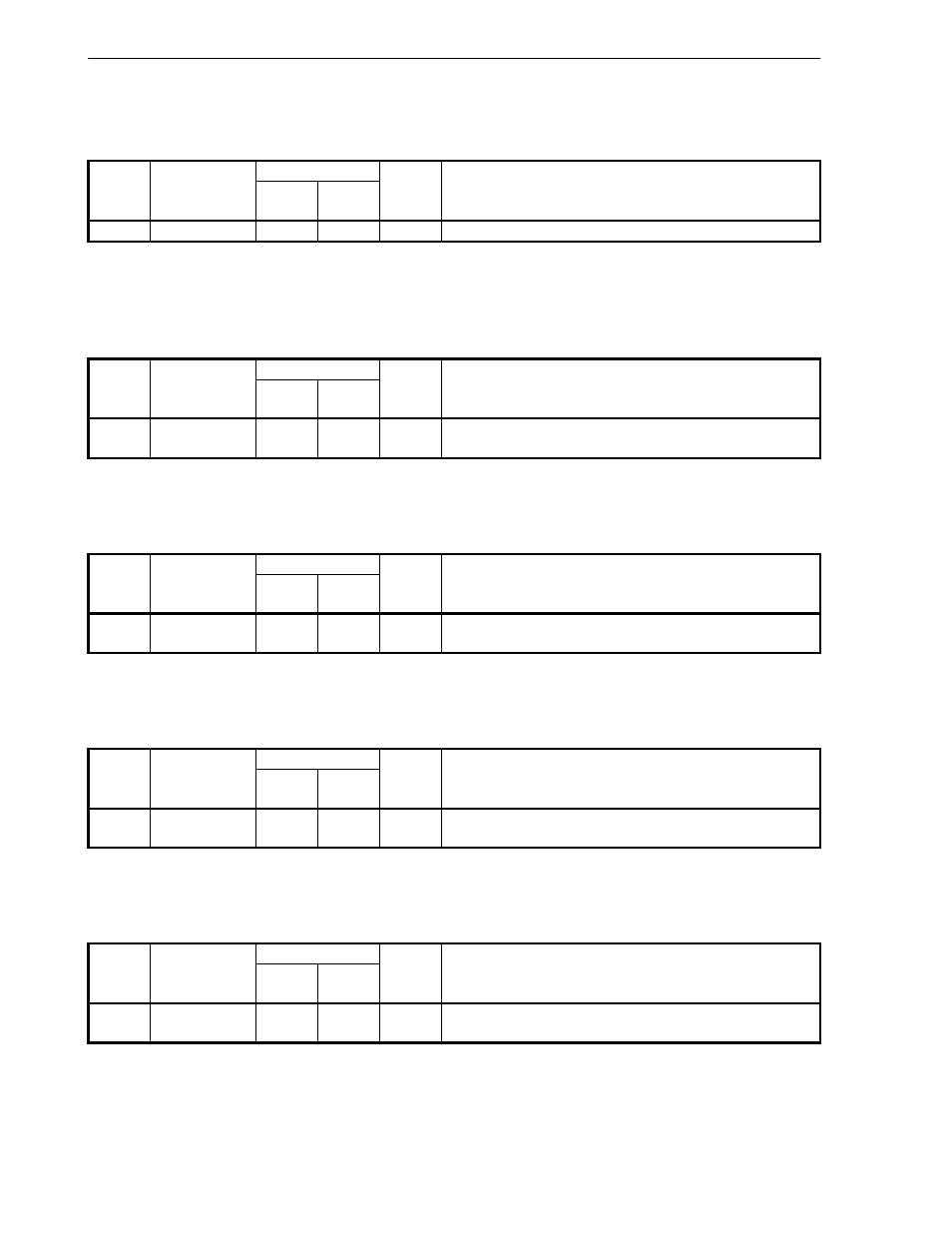

7.5.19.14 Subsystem ID register

This register is used to uniquely identify the expansion board or subsystem where the PCI device resides.

R/W

Bits

Field

Internal

bus

PCI

Default

Description

15:0

Subsystem ID

R/W

R

0

The V

R

4120A should set the identifier to this register.

7.5.19.15 Cap_Ptr register

This register is used to show a linked list of new capabilities implemented by The PCI Controller. The PCI

Controller has PPMI function as a new capability. Its data structure starts from ‘40H’ in the configuration register.

R/W

Bits

Field

Internal

bus

PCI

Default

Description

7:0

Capabilities

Pointer

R

R

40H

Hardwired to ‘40H’, where is the first term of the new capabilities

list.

7.5.19.16 Interrupt line register

The Interrupt Line register is used to communicate interrupt line routing information.

R/W

Bits

Field

Internal

bus

PCI

Default

Description

7:0

Interrupt Line

R/W

R/W

0

The value in this register shows the input of the system interrupt

controller that the interrupt pin is connected.

7.5.19.17 Interrupt pin register

This register tells which interrupt pin the PCI Controller uses.

R/W

Bits

Field

Internal

bus

PCI

Default

Description

7:0

Interrupt Pin

R

R

01H

Hardwired to ‘01H’, which means the PCI Controller uses INTA_B

pin.

7.5.19.18 Min_Gnt register

This register specifies how long a burst period the PCI Controller needs assuming a clock rate of 33MHz.

R/W

Bits

Field

Internal

bus

PCI

Default

Description

7:0

Min_Gnt

R/W

R

0

The user of the PCI Controller must prepare the value to this

register. The value should be set by the V

R

4120A.