3 registers, 1 register map – NEC Network Controller uPD98502 User Manual

Page 415

CHAPTER 8 UART

Preliminary User’s Manual S15543EJ1V0UM

415

8.3 Registers

This controller uses the NEC NA16550L Mega-Function as its internal UART. This UART is functionally identical to

the National Semiconductor NS16550D. Refer to the NEC “User’s Manual. Mega FunctionNA16550L” for more

information and programming details.

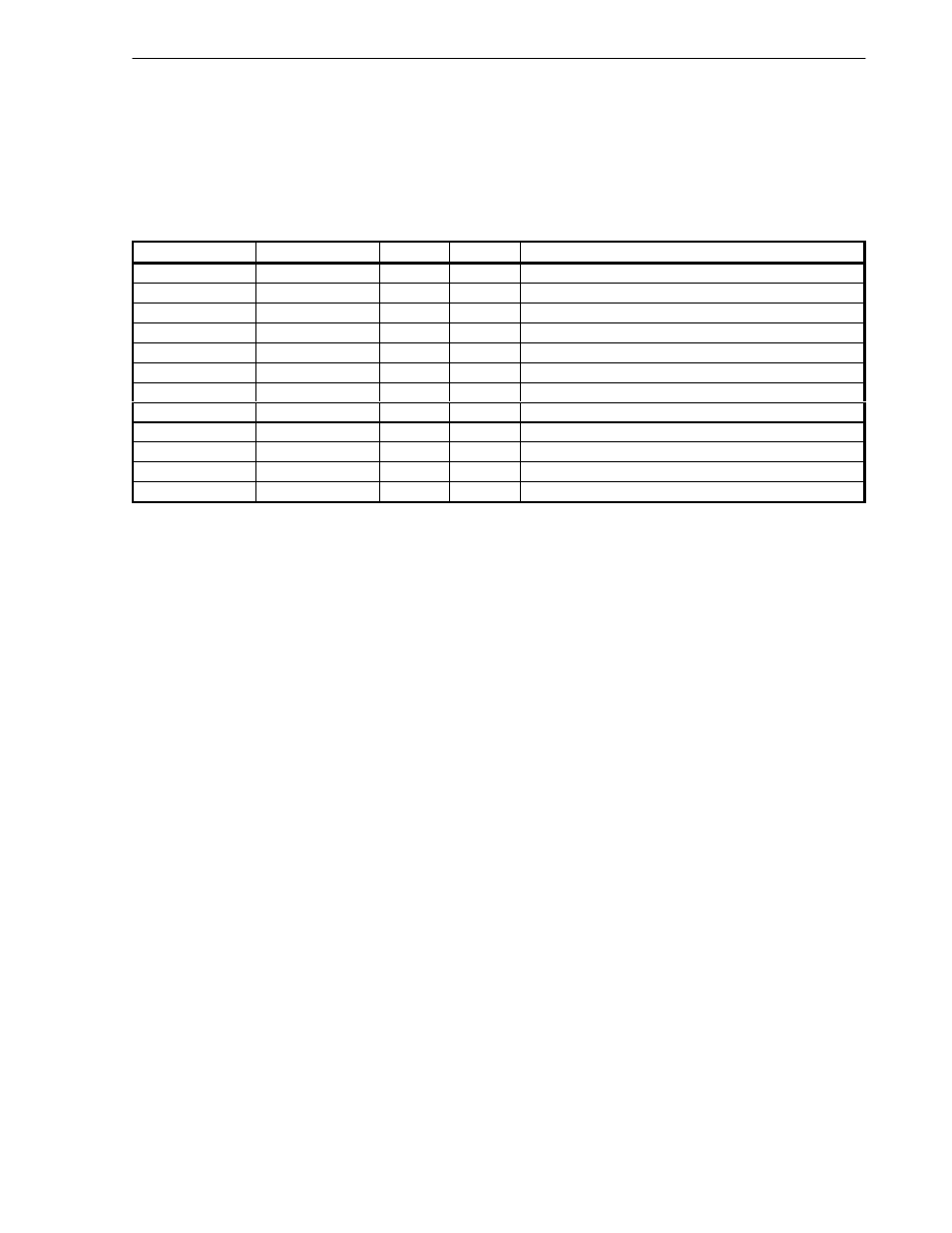

8.3.1 Register map

Offset Address

Register Name

R/W

Access

Description

1000_0080H

UARTRBR

R

W/H/B

UART, Receiver Buffer Register [DLAB=0,READ]

1000_0080H

UARTTHR

W

W/H/B

UART, Transmitter Holding Register [DLAB=0,WRITE]

1000_0080H

UARTDLL

R/W

W/H/B

UART, Divisor Latch LSB Register [DLAB=1]

1000_0084H

UARTIER

R/W

W/H/B

UART, Interrupt Enable Register [DLAB=0]

1000_0084H

UARTDLM

R/W

W/H/B

UART, Divisor Latch MSB Register [DLAB=1]

1000_0088H

UARTIIR

R

W/H/B

UART, Interrupt ID Register [READ]

1000_0088H

UARTFCR

W

W/H/B

UART, FIFO control Register [WRITE]

1000_008CH

UARTLCR

R/W

W/H/B

UART, Line control Register

1000_0090H

UARTMCR

R/W

W/H/B

UART, Modem Control Register

1000_0094H

UARTLSR

R/W

W/H/B

UART, Line status Register

1000_0098H

UARTMSR

R/W

W/H/B

UART, Modem Status Register

1000_009CH

UARTSCR

R/W

W/H/B

UART, Scratch Register

Remarks 1. In the “R/W” field,

“W” means “writeable”,

“R” means “readable”,

“RC” means “read-cleared”,

“- “ means “not accessible”.

2. All internal registers are 32-bit word-aligned registers.

3. The burst access to the internal register is prohibited.

If such burst access has been occurred, IRERR bit in NSR is set and NMI will assert to CPU.

4. Read access to the reserved area will set the CBERR bit in the NSR register and the dummy read

response data with the data-error bit set on SysCMD [0] is returned.

5. Write access to the reserved area will set the CBERR bit in the NSR register, and the write data is lost.

6. In the “Access” filed,

“W” means that word access is valid,

“H” means that half word access is valid,

“B” means that byte access is valid.

7. Write access to the read-only register cause no error, but the write data is lost.

8. The CPU can access all internal registers, but IBUS master device cannot access them.