7 sdmdr (sdram mode register) – NEC Network Controller uPD98502 User Manual

Page 209

CHAPTER 3 SYSTEM CONTROLLER

Preliminary User’s Manual S15543EJ1V0UM

209

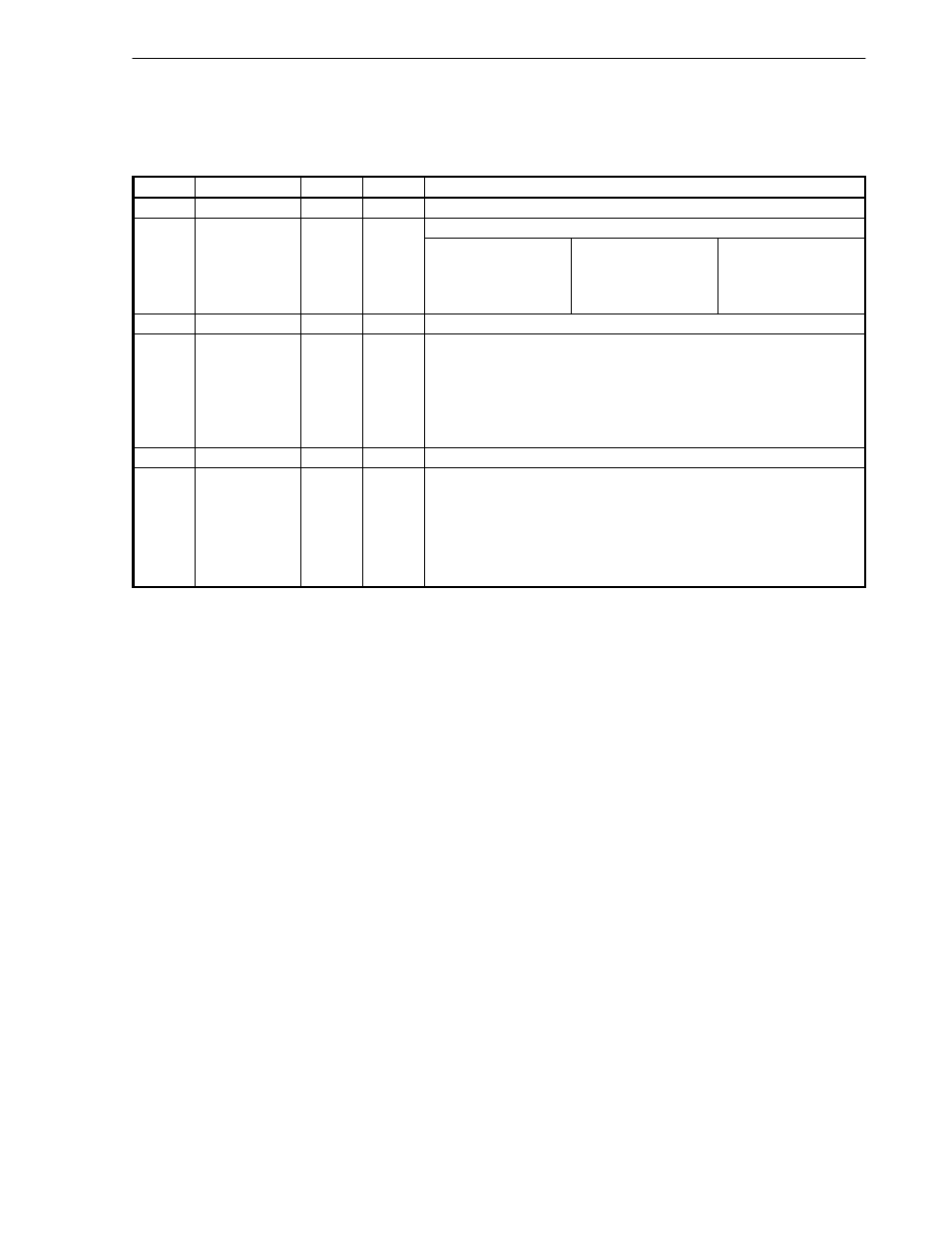

3.4.7 SDMDR (SDRAM Mode Register)

The SDRAM mode register “SDMDR” is a read-write and 32-bit word-aligned register. SDMDR is used to setup the

SDRAM interface. SDMDR is initialized to 330H at reset and contains the following fields:

Bits

Field

R/W

Default

Description

31:10

Reserved

R/W

0

Hardwired to 0.

SDRAM RAS-CAS delay:

9:8

RCD

R/W

11

00 = reserved

01 = 2 clocks

10 = 3 clocks

11 = 4 clocks (default)

66 MHz: 30.3 ns

66 MHz: 45.5 ns

66 MHz: 60.6 ns

100 MHz: 20 ns

100 MHz: 30 ns

100 MHz: 40 ns

7

Reserved

R/W

0

Hardwired to 0.

6:4

LTMD

R/W

011

SDRAM CAS latency:

000 = reserved

001 = reserved

010 = 2

011 = 3 (default)

1xx = reserved

3

Reserved

R/W

0

Hardwired to 0.

2:0

BL

R/W

000

SDRAM burst length:

000 = 1 (default)

001 = reserved

010 = reserved

011 = reserved

1xx = reserved

Remarks 1. RAS-CAS delay time is depended on the system clock frequency.

2. Don’t change the value on this register after using the SDRAM.

3. The initialization by setting this register must be done before using the SDRAM.