5 registers, 1 register map – NEC Network Controller uPD98502 User Manual

Page 390

CHAPTER 7 PCI CONTROLLER

390

Preliminary User’s Manual S15543EJ1V0UM

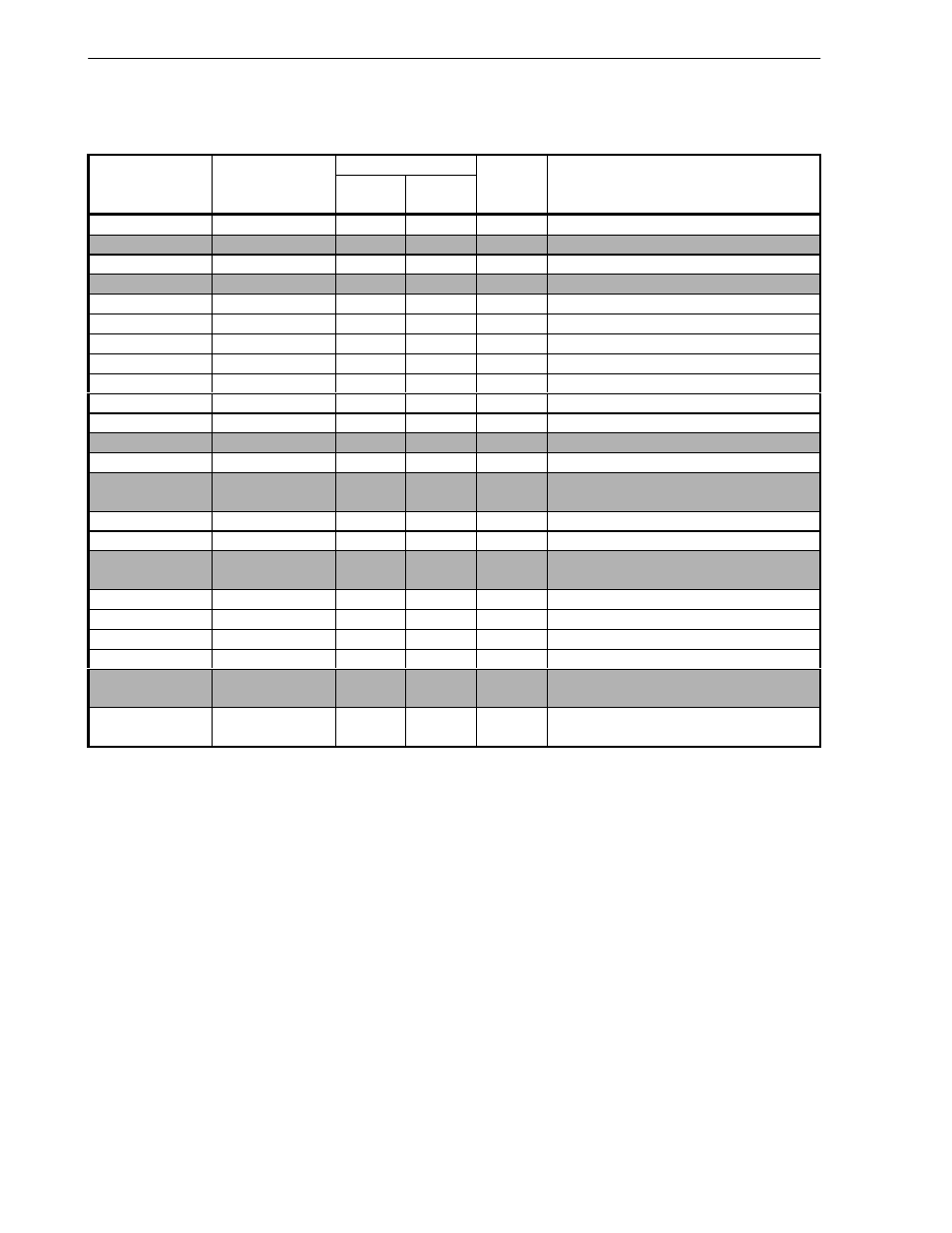

7.5 Registers

7.5.1 Register map

R/W

Offset Address

Register Name

Internal

bus

PCI

Access

Description

1000_4000H

P_PLBA

R/W

R/W

W/H/B

PCI Lower Base Address Register

1000_4004H

N/A

-

-

-

Reserved

1000_4008H

P_IBBA

R/W

R/W

W/H/B

Internal Bus Base Address Register

1000_400CH

N/A

-

-

-

Reserved

1000_4010H

P_VERR

R

R

W/H/B

Version Register

1000_4014H

P_PCAR

R/W

R

W/H/B

PCI Configuration Address Register

1000_4018H

P_PCDR

R/W

R

W/H/B

PCI Configuration Data Register

1000_401CH

P_IGSR

RC

R/W

W

Internal Bus General Status Register

1000_4020H

P_IIMR

R/W

R/W

W/H/B

Internal Bus Interrupt Mask Register

1000_4024H

P_PGSR

R/W

RC

W

PCI General Status Register

1000_4028H

P_PIMR

R/W

R/W

W/H/B

PCI Interrupt Mask Register

1000_402CH

N/A

-

-

-

Reserved

1000_4030H

P_HMCR

R/W

R/W

W/H/B

Host Mode Control Register

1000_4034H:

1000_403CH

N/A

-

-

-

Reserved

1000_4040H

P_PWCD

R/W

R

W/H/B

Power Consumption Data Register

1000_4044H

P_PWDD

R/W

R

W/H/B

Power Dissipation Data Register

1000_4048H:

1000_404CH

N/A

-

-

-

Reserved

1000_4050H

P_BCNT

R/W

R/W

W/H/B

Bridge Control Register

1000_4054H

P_PPCR

R/W

R

W/H/B

Power Control Register

1000_4058H

P_SWRR

-

W

W

Software Reset Register

1000_405CH

P_RTMR

R/W

R/W

W/H/B

Retry Timer register

1000_4060H:

1000_40FCH

N/A

-

-

-

Reserved

1000_4100H:

1000_41FCH

P_CONFIG

See

7.5.19

See

7.5.19

W/H/B

PCI Configuration Registers

Remarks 1. In the “R/W” field,

“W” means “writeable”,

“R” means “readable”,

“RC” means “read-cleared”,

“- “ means “not accessible”.

2. All internal registers are 32-bit word-aligned registers.

3. The burst access to the internal register is prohibited.

If such burst access has been occurred, IRERR bit in NSR is set and NMI will assert to CPU.

4. Read access to the reserved area will set the CBERR bit in the NSR register and the dummy read

response data with the data-error bit set on SysCMD [0] is returned.

5. Write access to the reserved area will set the CBERR bit in the NSR register, and the write data is lost.

6. In the “Access” filed,

“W” means that word access is valid,

“H” means that half word access is valid,

“B” means that byte access is valid.

7. Write access to the read-only register cause no error, but the write data is lost.

8. The CPU can access all internal registers, but IBUS master device cannot access them.