NEC Network Controller uPD98502 User Manual

Page 73

CHAPTER 2 V

R

4120A

Preliminary User’s Manual S15543EJ1V0UM

73

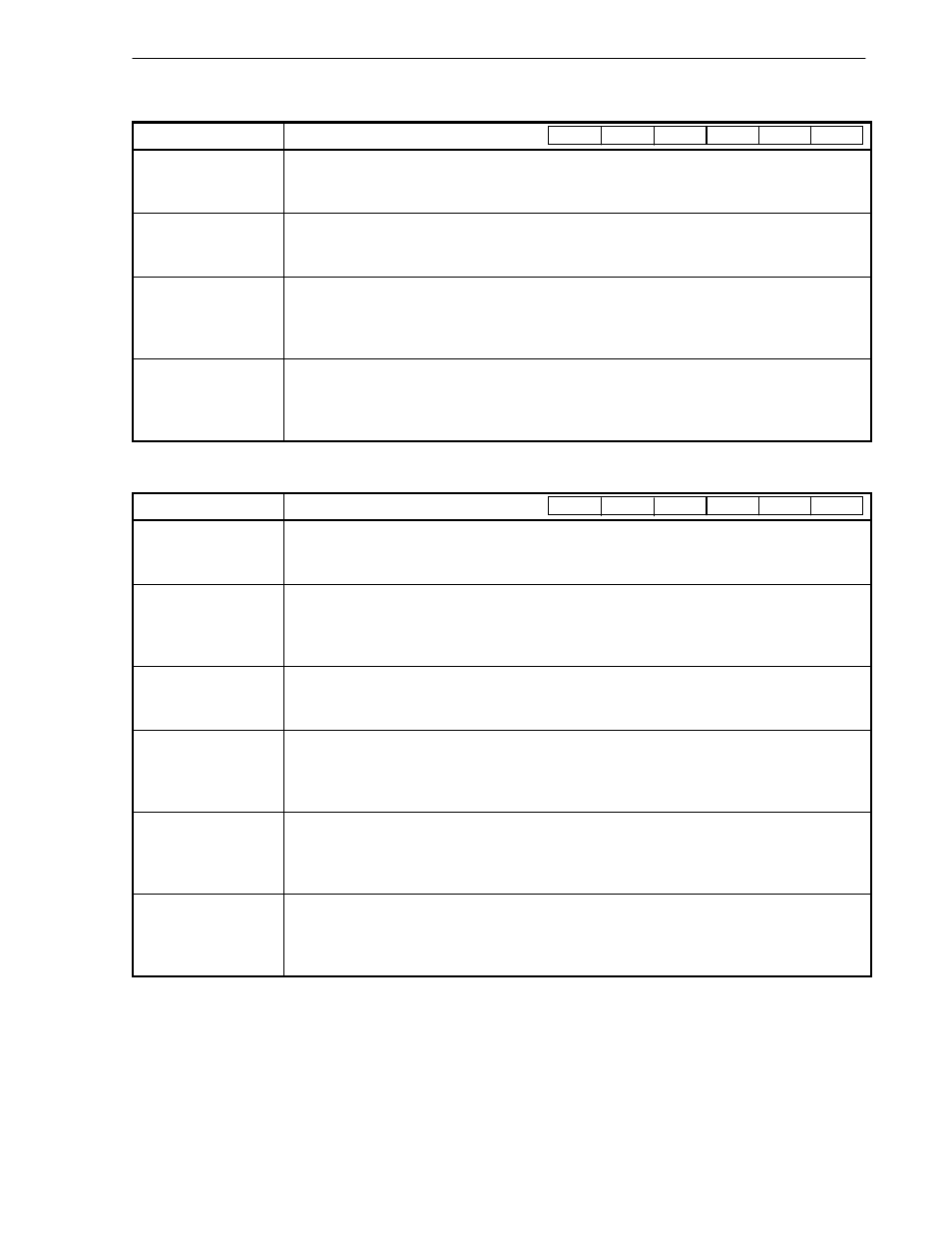

Table 2-9. Three-Operand Type Instruction (Extended ISA)

Instruction

Format and Description

Doubleword Add

DADD rd, rt, rs

The contents of register rs are added to that of register rt. The 64-bit result is stored into register rd.

An exception occurs on the generation of integer overflow.

Doubleword Add

Unsigned

DADDU rd, rt, rs

The contents of register rs are added to that of register rt. The 64-bit result is stored into register rd.

No exception occurs on the generation of integer overflow.

Doubleword Subtract

DSUB rd, rt, rs

The contents of register rt are subtracted from that of register rs. The 64-bit result is stored into

register rd.

An exception occurs on the generation of integer overflow.

Doubleword Subtract

Unsigned

DSUBU rd, rt, rs

The contents of register rt are subtracted from that of register rs. The 64-bit result is stored into

register rd.

No exception occurs on the generation of integer overflow.

Table 2-10. Shift Instruction

Instruction

Format and Description

Shift Left Logical

SLL rd, rs, sa

The contents of register rt are shifted left by sa bits and zeros are inserted into the emptied lower bits.

The 32-bit result is stored into register rd. In the 64-bit mode, the operand must be sign extended.

Shift Right Logical

SRL rd, rs, sa

The contents of register rt are shifted right by sa bits and zeros are inserted into the emptied higher

bits.

The 32-bit result is stored into register rd. In the 64-bit mode, the operand must be sign extended.

Shift Right Arithmetic

SRA rd, rt, sa

The contents of register rt are shifted right by sa bits and the emptied higher bits are sign extended.

The 32-bit result is stored into register rd. In the 64-bit mode, the operand must be sign extended.

Shift Left Logical

Variable

SLLV rd, rt, rs

The contents of register rt are shifted left and zeros are inserted into the emptied lower bits. The lower

five bits of register rs specify the shift count.

The 32-bit result is stored into register rd. In the 64-bit mode, the operand must be sign extended.

Shift Right Logical

Variable

SRLV rd, rt, rs

The contents of register rt are shifted right and zeros are inserted into the emptied higher bits. The

lower five bits of register rs specify the shift count.

The 32-bit result is stored into register rd. In the 64-bit mode, the operand must be sign extended.

Shift Right Arithmetic

Variable

SRAV rd, rt, rs

The contents of register rt are shifted right and the emptied higher bits are sign extended. The lower

five bits of register rs specify the shift count.

The 32-bit result is stored into register rd. In the 64-bit mode, the operand must be sign extended.

op

rs

rt

funct

rd

sa

op

rs

rt

funct

rd

sa