4 u_gsr1 (usb general status register 1) – NEC Network Controller uPD98502 User Manual

Page 314

CHAPTER 6 USB CONTROLLER

314

Preliminary User’s Manual S15543EJ1V0UM

6.2.4

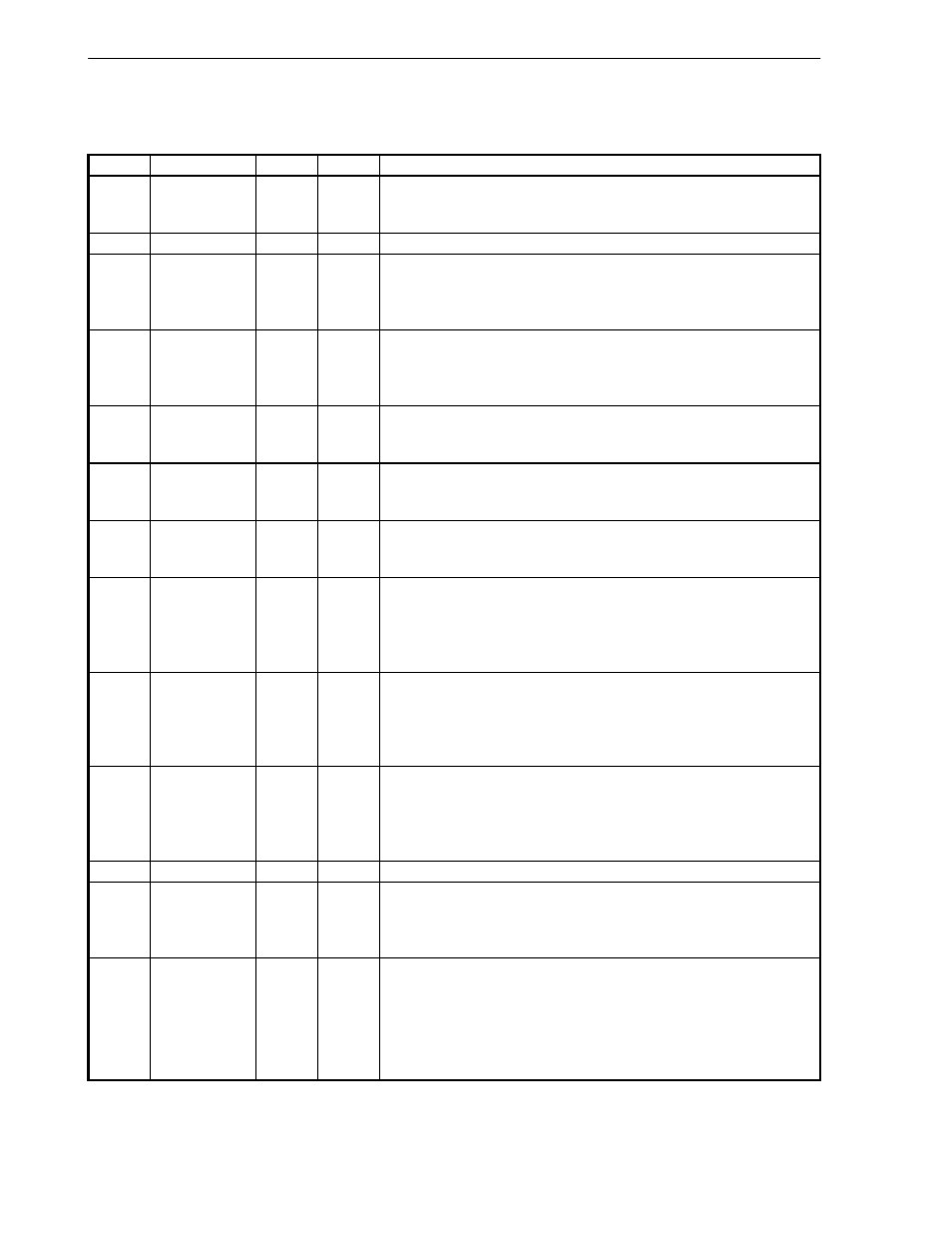

U_GSR1 (USB General Status Register 1)

This register indicates the current status of USB Controller.

Bits

Field

R/W

Default

Description

31

GSR2

RC

0

If some bits of General Status Register 2 are set to ‘1’s and the

corresponding bits in Interrupt Mask Register 2 are set to ‘1’s, this GSR2 bit

will be set to a ‘1’.

30:24

Reserved

R

0

Reserved for future use

23

TMF

RC

0

Tx MailBox Full:

Bit that indicates transmit MailBox area is full. This bit is set to a ‘1’ when the

USB Tx MailBox Read Address and the USB Tx MailBox Write Address get

equal. This bit is reset to a ‘0’ when the V

R

4120A reads this register.

22

RMF

RC

0

Rx MailBox Full:

Bit that indicates receive MailBox area is full. This bit is set to a ‘1’ when the

USB Rx MailBox Read Address and the USB Rx MailBox Write Address get

equal. This bit is reset to a ‘0’ when the V

R

4120A reads this register.

21

RPE2

RC

0

Rx Pool2 Empty:

Bit that indicates receive Pool2 is empty.

This bit is reset to a ‘0’ when the V

R

4120A reads this register.

20

RPE1

RC

0

Rx Pool1 Empty:

Bit that indicates receive Pool1 is empty.

This bit is reset to a ‘0’ when the V

R

4120A reads this register.

19

RPE0

RC

0

Rx Pool0 Empty:

Bit that indicates receive Pool0 is empty.

This bit is reset to a ‘0’ when the V

R

4120A reads this register.

18

RPA2

RC

0

Rx Pool2 Alert:

This bit is set to a ‘1’ when the number of Buffer Directories remaining in

receive Pool2 gets equal to 4 times of the AL field value in the Rx Pool2

Information Register.

This bit is reset to a ‘0’ when the V

R

4120A reads this register.

17

RPA1

RC

0

Rx Pool1 Alert:

This bit is set to a ‘1’ when the number of Buffer Directories remaining in

receive Pool1 gets equal to 4 times of the AL field value in the Rx Pool1

Information Register.

This bit is reset to a ‘0’ when the V

R

4120A reads this register.

16

RPA0

RC

0

Rx Pool0 Alert:

This bit is set to a ‘1’ when the number of Buffer Directories remaining in

receive Pool0 gets equal to 4 times of the AL field value in the Rx Pool0

Information Register.

This bit is reset to a ‘0’ when the V

R

4120A reads this register.

15:11

Reserved

R

0

Reserved for future use

10

DER

RC

0

DMA Error:

Bit that indicates that an error occurred during DMA transfer. This bit is set to

a ‘1’ if an error occurs on the Internal BUS during DMA transfer.

This bit is reset to a ‘0’ when the V

R

4120A reads this register.

9

EP2FO

RC

0

EP2 FIFO Error:

Bit that indicates that an overrun has occurred for the FIFO of EndPoint2

(Isochronous OUT). When the FIFO becomes full while EndPoint2 is

performing a transaction, USB Controller can no longer receive data and all

data subsequent is discarded. Should this occur, this bit is set to a ‘1’.

This bit is reset to a ‘0’ when the V

R

4120A reads this register.