NEC Network Controller uPD98502 User Manual

Page 137

CHAPTER 2 V

R

4120A

Preliminary User’s Manual S15543EJ1V0UM

137

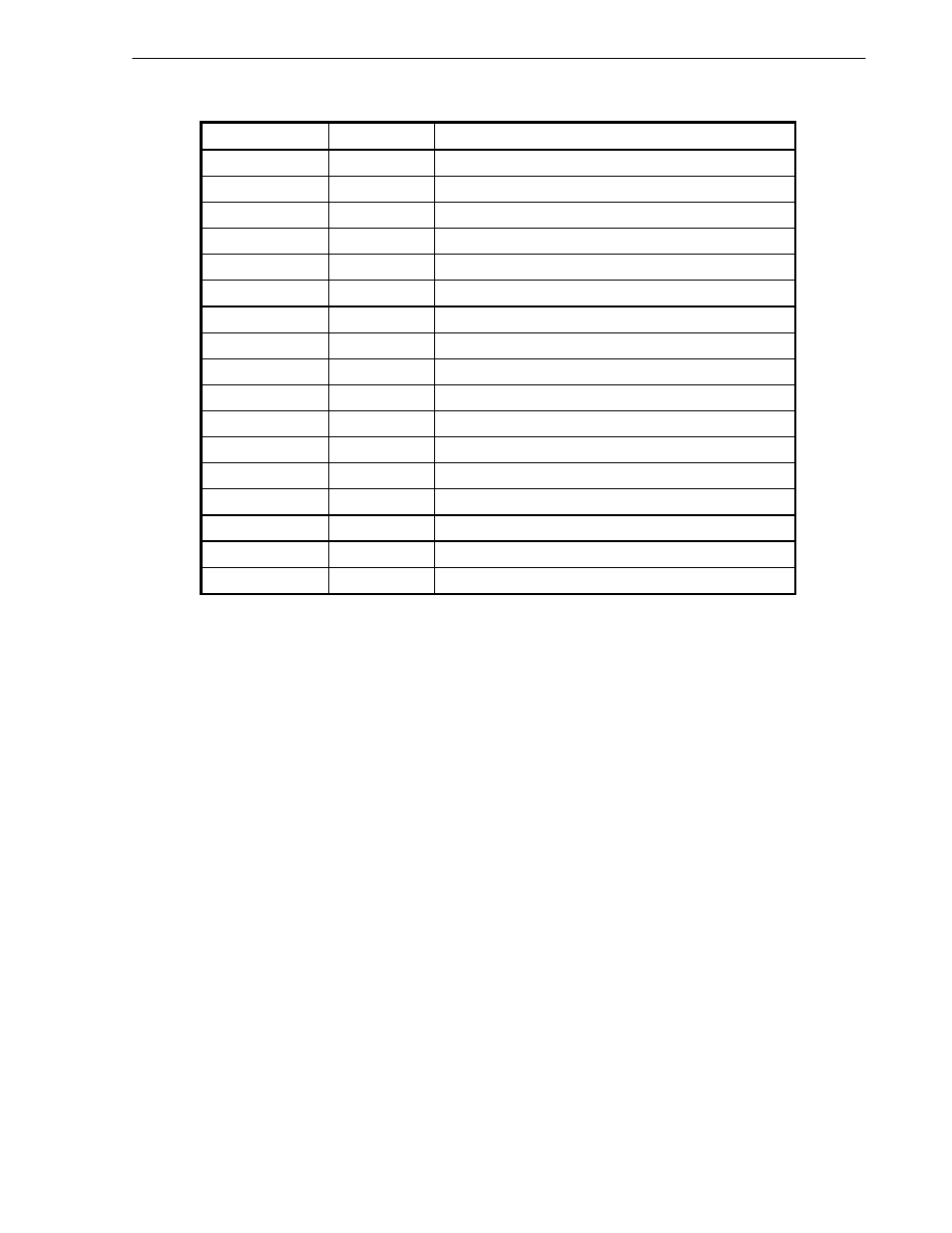

Table 2-35. Cause Register Exception Code Field

Exception Code

Mnemonic

Description

0

Int

Interrupt exception

1

Mod

TLB Modified exception

2

TLBL

TLB Refill exception (load or fetch)

3

TLBS

TLB Refill exception (store)

4

AdEL

Address Error exception (load or fetch)

5

AdES

Address Error exception (store)

6

IBE

Bus Error exception (instruction fetch)

7

DBE

Bus Error exception (data load or store)

8

Sys

System Call exception

9

Bp

Breakpoint exception

10

RI

Reserved Instruction exception

11

CpU

Coprocessor Unusable exception

12

Ov

Integer Overflow exception

13

Tr

Trap exception

14 to 22

RFU

23

WATCH

Watch exception

24 to 31

RFU

The V

R

4120A CPU has eight interrupt request sources, IP7 to IP0. For the detailed description of interrupts, refer

to Section 2.8 CPU Core Interrupts.

(1) IP7

This bit indicates whether there is a timer interrupt request.

It is set when the values of Count register and Compare register match.

(2) IP6 to IP2

IP6 to IP2 reflect the state of the interrupt request signal of the CPU core.

(3) IP1 and IP0

These bits are used to set/clear a software interrupt request.