Store doubleword right (1/3) – NEC Network Controller uPD98502 User Manual

Page 543

APPENDIX A MIPS III INSTRUCTION SET DETAILS

Preliminary User’s Manual S15543EJ1V0UM

543

SDR

Store Doubleword Right (1/3)

SDR

base

SDR

1 0 1 1 0 1

rt

offset

31

26 25

21 20

16 15

0

6

5

5

16

Format:

SDR rt, offset (base)

Description:

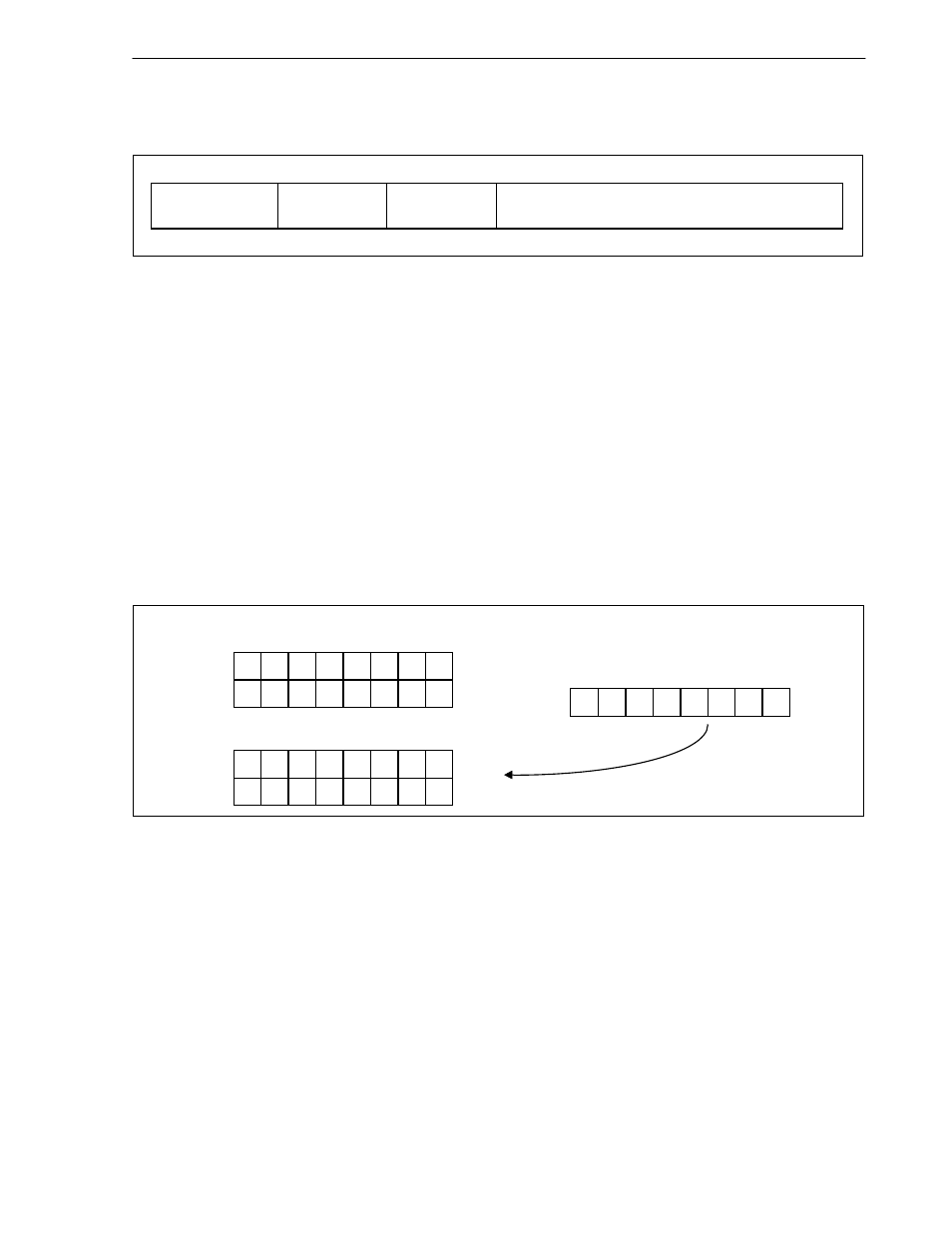

This instruction can be used with the SDL instruction to store the contents of a register into eight consecutive bytes

of memory, when the bytes cross a boundary between two doublewords. SDR stores the register into the

appropriate part of the low-order doubleword; SDL stores the register into the appropriate part of the low-order

doubleword of memory.

The SDR instruction adds its sign-extended 16-bit

offset to the contents of general register base to form a virtual

address that may specify an arbitrary byte. It alters only the word in memory that contains that byte. From one to

eight bytes will be stored, depending on the starting byte specified.

Conceptually, it starts at the least-significant byte of the register and copies it to the specified byte in memory; then

it copies bytes from register to memory until it reaches the high-order byte of the word in memory. No address

error exceptions due to alignment are possible.

address 8

address 0

memory

15 14 13 12 11 10

9

8

7

6

5

4

3

2

1

0

A

B

C

D

E

F

G

H

before

after

$24

register

SDR $24, 1 ($0)

address 8

address 0

15 14 13 12 11 10

9

8

B

C

D

E

F

G

H

0