NEC Network Controller uPD98502 User Manual

Page 372

CHAPTER 7 PCI CONTROLLER

372

Preliminary User’s Manual S15543EJ1V0UM

7.2.1.3 Write issue from internal bus to PCI

(1) Posted write transaction

If IPWRD bit in P_BCNT register is ‘0’, the PCI Controller uses “Posted Write Transaction” rule for write

transactions from the internal bus-side to PCI-side. The rule is as follows;

<1> An internal bus block

Note

connecting to the internal bus issues the write transaction to PCI target device.

<2> The PCI Controller accepts this access and puts the data to be written into the internal FIFO. The

transaction on internal bus is completed at this moment. Then, the PCI Controller will issues “retry” to all of

later write access on internal bus to external PCI devices until the write transaction on PCI bus has been

completed.

<3> The PCI Controller issues the write transaction to PCI target device.

<4> After the completion of the transaction, the PCI Controller can accepts the new write transaction on internal

bus again.

Note

Internal bus block is a block connecting to the internal bus like USB controller. All of other internal bus

devices than the PCI Controller can issue access cycle to external PCI devices. The V

R

4120A can also

issue access cycles to the PCI devices through the system controller.

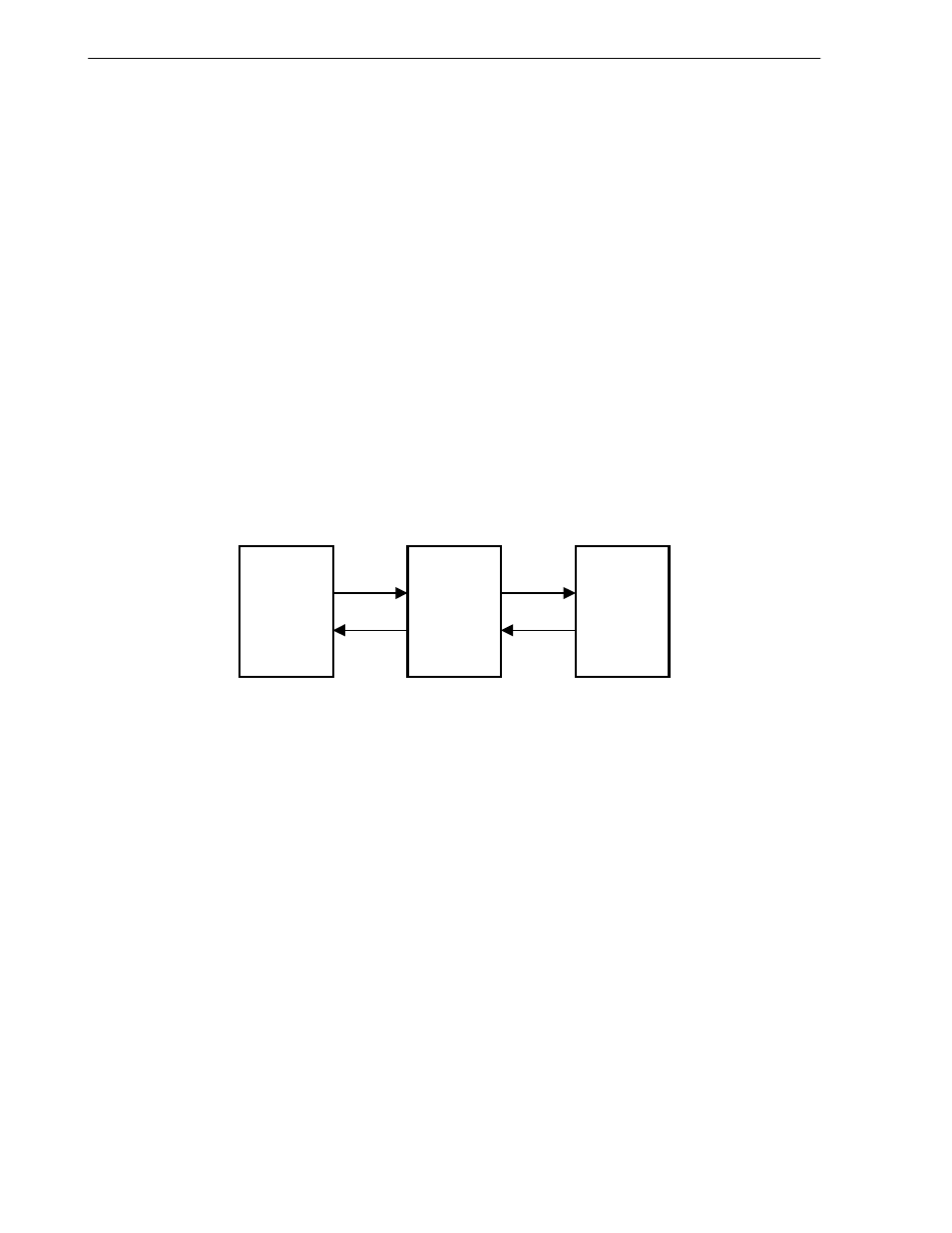

Figure 7-2. Posted Write Transaction from Internal Bus to PCI

PCI

Controller

PCI

Target

Device

Internal

Bus Block

<1>

<2>

<3>

<4>

The maximum burst size is 16 words. When more than 16 words write burst is issued on Internal bus, the PCI

Controller issues “disconnect” at 16th word. In the case of a burst access across the address boundary, the PCI

Controller issues “disconnect”, too.

When the PCI Controller receives target abort/master abort on PCI bus after it accepts posted-write from Internal

bus-side, it sets WRTAT/WRMAT bit of P_IGSR register and RTABT/RMABT bit of P_PGSR register, and issues an

interrupt to PCI-Host and the V

R

4120A (if not masked). The data in the internal FIFO will be discarded. Then, the PCI

Controller can accept the new write transaction on the internal bus.