15 en_madr (mii address register), 16 en_mwtd (mii write data register), 17 en_mrdd (mii read data register) – NEC Network Controller uPD98502 User Manual

Page 289: 18 en_mind (mii indicate register)

CHAPTER 5 ETHERNET CONTROLLER

Preliminary User’s Manual S15543EJ1V0UM

289

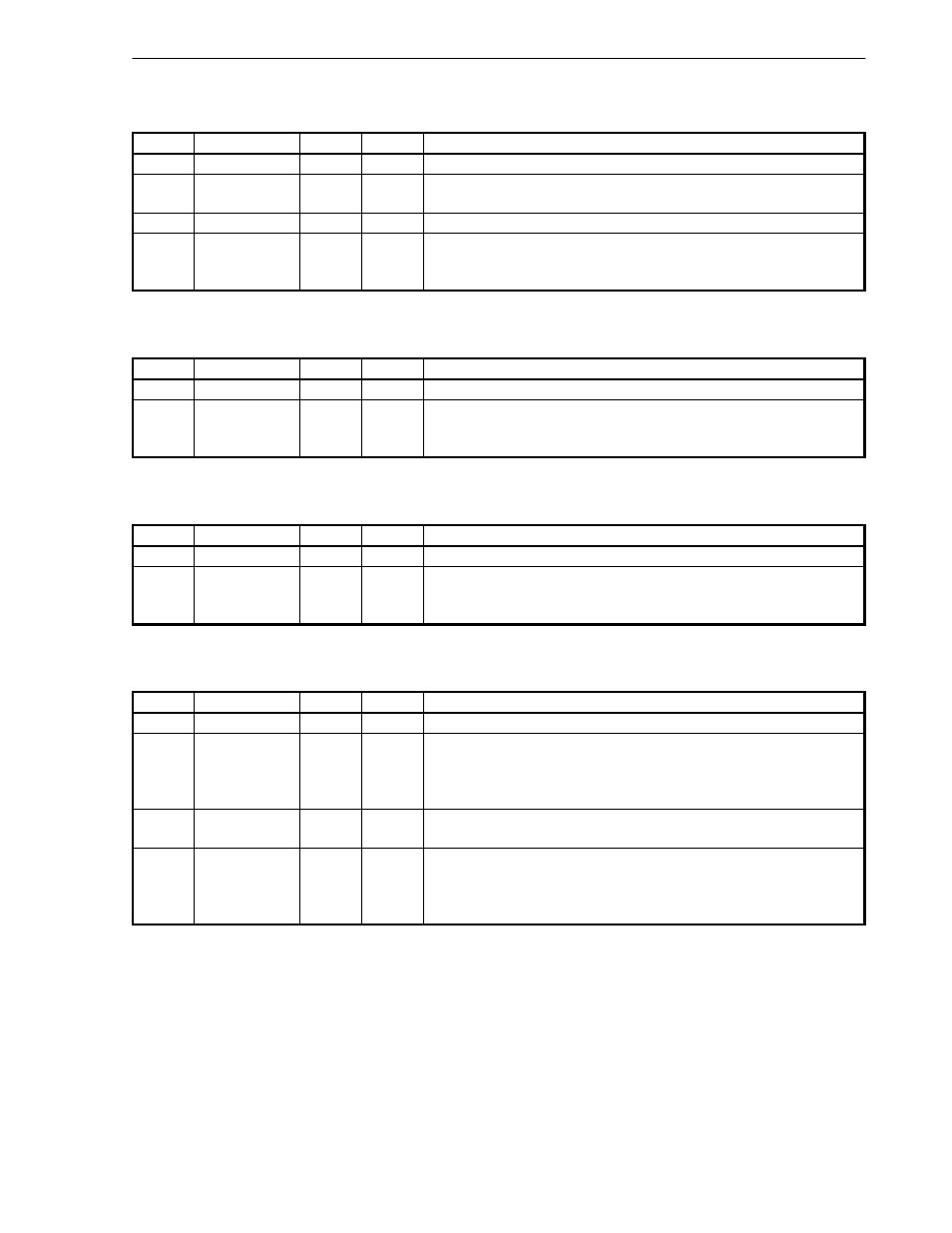

5.2.15 En_MADR (MII Address Register)

Bits

Field

R/W

Default

Description

31:13

Reserved

R/W

0

Reserved for future use. Write 0s.

12:8

FIAD

R/W

0

MII PHY address:

This field sets PHY address to be selected during the management access.

7:5

Reserved

R/W

0

Reserved for future use. Write 0s.

4:0

RGAD

R/W

0

MII register address:

This field sets register address to be accessed during the management

access.

5.2.16 En_MWTD (MII Write Data Register)

Bits

Field

R/W

Default

Description

31:16

Reserved

R/W

0

Reserved for future use. Write 0s.

15:0

CTLD

R/W

0

MII write data:

This field sets the MII management write data for write access through the

MII management interface.

5.2.17 En_MRDD (MII Read Data Register)

Bits

Field

R/W

Default

Description

31:16

Reserved

R

0

Reserved for future use.

15:0

CTLD

R

0

MII read data:

This field indicates the MII management read data for read access through

the MII management interface.

5.2.18 En_MIND (MII Indicate Register)

Bits

Field

R/W

Default

Description

31:3

Reserved

R

0

Reserved for future use.

2

NVALID

R

0

SCAN command start status:

This bit is set to a ‘1’ when SCANC bit in En_MCMD register is set to 1.

When the first read access using the SCAN command is completed, this bit

is cleared.

1

SCANA

R

0

SCAN command active:

This bit is set to a ‘1’ while SCANC bit in En_MCMD register is set to 1.

0

BUSY

R

0

BUSY:

This bit indicates that the MAC Control Block is executing a management

access to a external PHY device through the MII management interface. This

bit is set to a ‘1’ during the management access.