NEC Network Controller uPD98502 User Manual

Page 123

CHAPTER 2 V

R

4120A

Preliminary User’s Manual S15543EJ1V0UM

123

2.4.5.6 EntryHi register (10)

The EntryHi register is write-accessible. It is used to access the on-chip TLB. The EntryHi register holds the high-

order bits of a TLB entry for TLB read and write operations. If a TLB Mismatch, TLB Invalid, or TLB Modified

exception occurs, the EntryHi register holds the high-order bit of the TLB entry. The EntryHi register is also set with

the virtual page number (VPN2) for a virtual address where an exception occurred and the ASID. See Section 2.5

Exception Processing for details of the TLB exception.

The ASID is used to read from or write to the ASID field of the TLB entry. It is also checked with the ASID of the

TLB entry as the ASID of the virtual address during address translation.

The EntryHi register is accessed by the TLBP, TLBWR, TLBWI, and TLBR instructions.

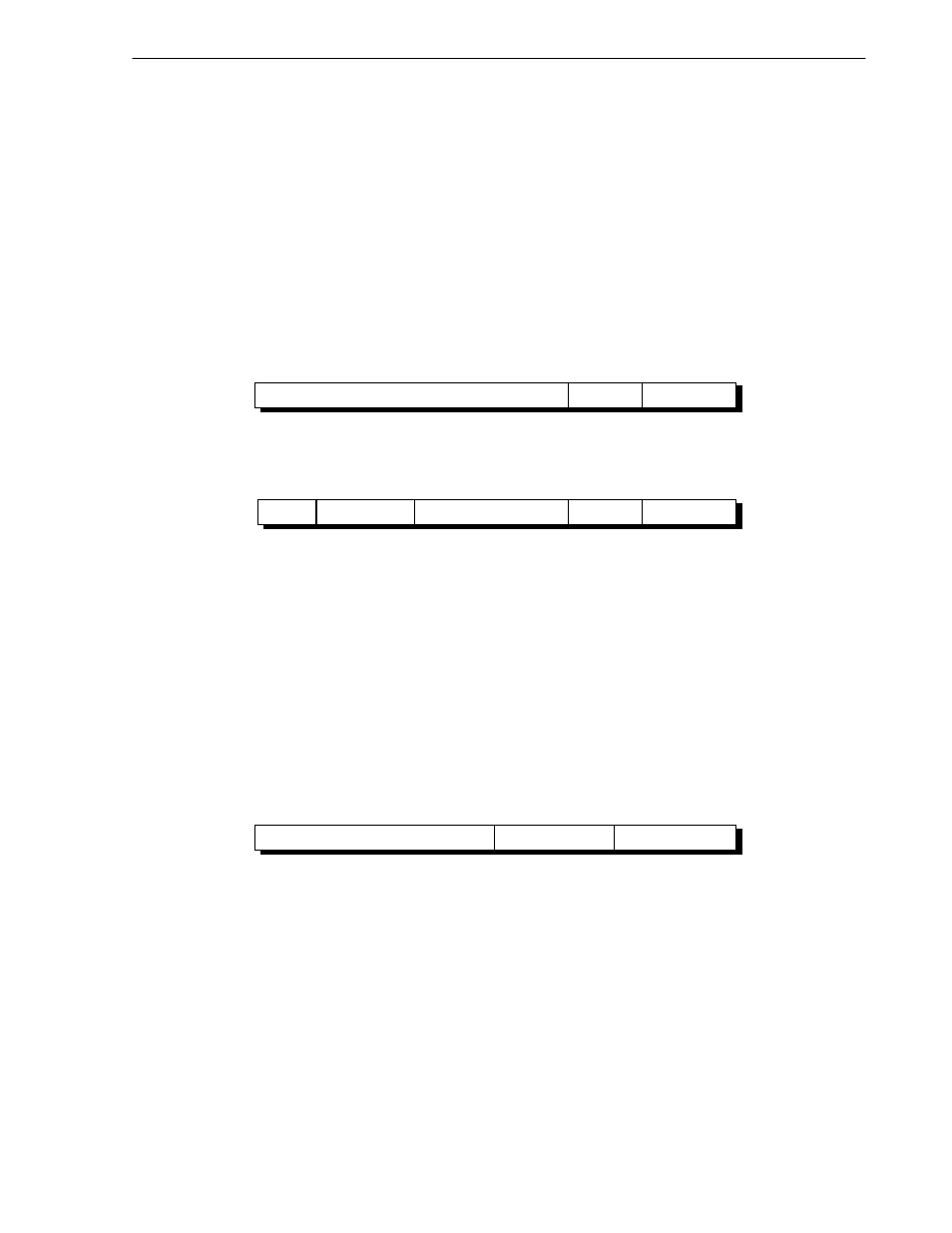

Figure 2-40. EntryHi Register

39

40

(a) 32-bit mode

8

3

21

0

31

11

10

8

7

VPN2

0

ASID

(b) 64-bit mode

62

61

8

3

2

22

29

0

63

11

10

8

7

R

Fill

VPN2

0

ASID

VPN2: Virtual page number divided by two (mapping to two pages)

ASID : Address space ID. An 8-bit ASID field that lets multiple processes share the TLB; each process has a

distinct mapping of otherwise identical virtual page numbers.

R

: Space type (00

→ user, 01 → supervisor, 11 → kernel). Matches bits 63 and 62 of the virtual address.

Fill

: RFU. Ignored on write. When read, returns zero.

0

: RFU. Write 0 in a write operation. When this field is read, 0 is read.

2.4.5.7 Processor revision identifier (PRId) register (15)

The 32-bit, read-only Processor Revision Identifier (PRId) register contains information identifying the

implementation and revision level of the CPU and CP0. Figure 2-41 shows the format of the PRId register.

Figure 2-41. PRId Register

15

16

7

8

0

31

0

Imp

Rev

16

8

8

Imp : CPU core processor ID number (0CH for the V

R

4120A)

Rev : CPU core processor revision number

0

: RFU. Write 0 in a write operation. When this field is read, 0 is read.

The processor revision number is stored as a value in the form y.x, where y is a major revision number in bits 7 to

4 and x is a minor revision number in bits 3 to 0.

The processor revision number can distinguish some CPU core revisions, however there is no guarantee that

changes to the CPU core will necessarily be reflected in the PRId register, or that changes to the revision number

necessarily reflect real CPU core changes. Therefore, create a program that does not depend on the processor

revision number area.