NEC Network Controller uPD98502 User Manual

Page 282

CHAPTER 5 ETHERNET CONTROLLER

282

Preliminary User’s Manual S15543EJ1V0UM

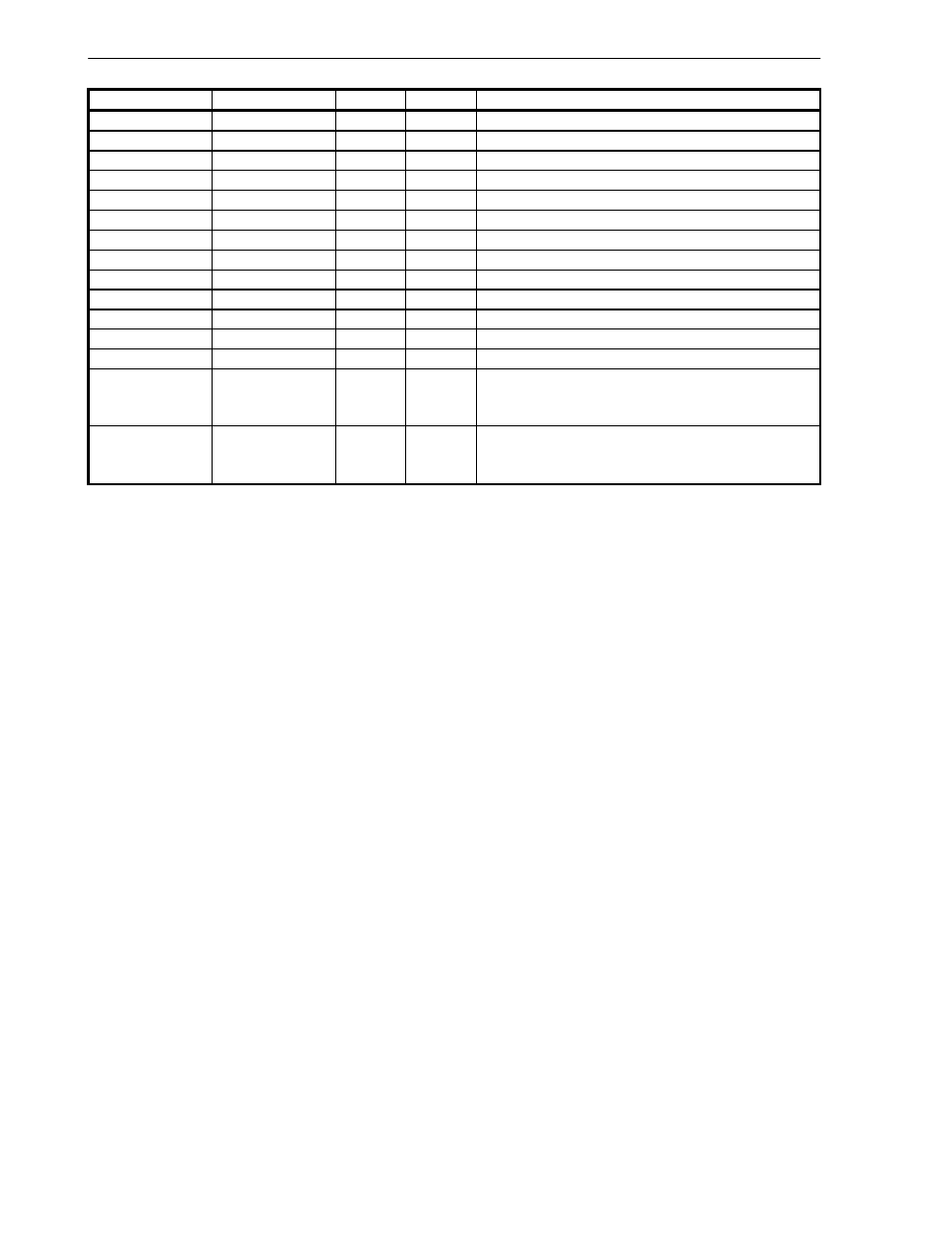

Offset Address

Register Name

R/W

Access

Description

1000_m1C4H

En_TPCT

R/W

W

Transmit Packet Counter

1000_m1C8H

En_TFCS

R/W

W

Transmit CRC Error Packet Counter

1000_m1CCH

En_TMCA

R/W

W

Transmit Multicast Packet Counter

1000_m1D0H

En_TBCA

R/W

W

Transmit Broadcast Packet Counter

1000_m1D4H

En_TUCA

R/W

W

Transmit Unicast Packet Counter

1000_m1D8H

En_TXPF

R/W

W

Transmit PAUSE control Frame Counter

1000_m1DCH

En_TDFR

R/W

W

Transmit Single Deferral Packet Counter

1000_m1E0H

En_TXDF

R/W

W

Transmit Excessive Deferral Packet Counter

1000_m1E4H

En_TSCL

R/W

W

Transmit Single Collision Packet Counter

1000_m1E8H

En_TMCL

R/W

W

Transmit Multiple collision Packet Counter

1000_m1ECH

En_TLCL

R/W

W

Transmit Late Collision Packet Counter

1000_m1F0H

En_TXCL

R/W

W

Transmit Excessive Collision Packet Counter

1000_m1F4H

En_TNCL

R/W

W

Transmit Total Collision Counter

1000_m1F8H

En_TCSE

R/W

W

Transmit Carrier Sense Error Counter

This counter is incremented for each frame transmitted

which carrier sense error occurs during transmission.

1000_m1FCH

En_TIME

R/W

W

Transmit Internal MAC Error Counter

This counter is incremented for each frame transmitted in

which an internal MAC error occurs during transmission.

Remarks 1. In the “Offset Address” field and in the “Register Name” field,

Ethernet Controller #1: m = 2, n = 1,

Ethernet Controller #2: m = 3, n = 2

2. In the “R/W” field,

“W” means “writeable”,

“R” means “readable”,

“RC” means “read-cleared”,

“- “ means “not accessible”.

3. All internal registers are 32-bit word-aligned registers.

4. The burst access to the internal register is prohibited.

If such burst access has been occurred, IRERR bit in NSR is set and NMI will assert to CPU.

5. Read access to the reserved area will set the CBERR bit in the NSR register and the dummy read

response data with the data-error bit set on SysCMD [0] is returned.

6. Write access to the reserved area will set the CBERR bit in the NSR register, and the write data is lost.

7. In the “Access” filed,

“W” means that word access is valid,

“H” means that half word access is valid,

“B” means that byte access is valid.

8. Write access to the read-only register cause no error, but the write data is lost.

9. The CPU can access all internal registers, but IBUS master device cannot access them.