2 registers, 1 register map – NEC Network Controller uPD98502 User Manual

Page 189

CHAPTER 3 SYSTEM CONTROLLER

Preliminary User’s Manual S15543EJ1V0UM

189

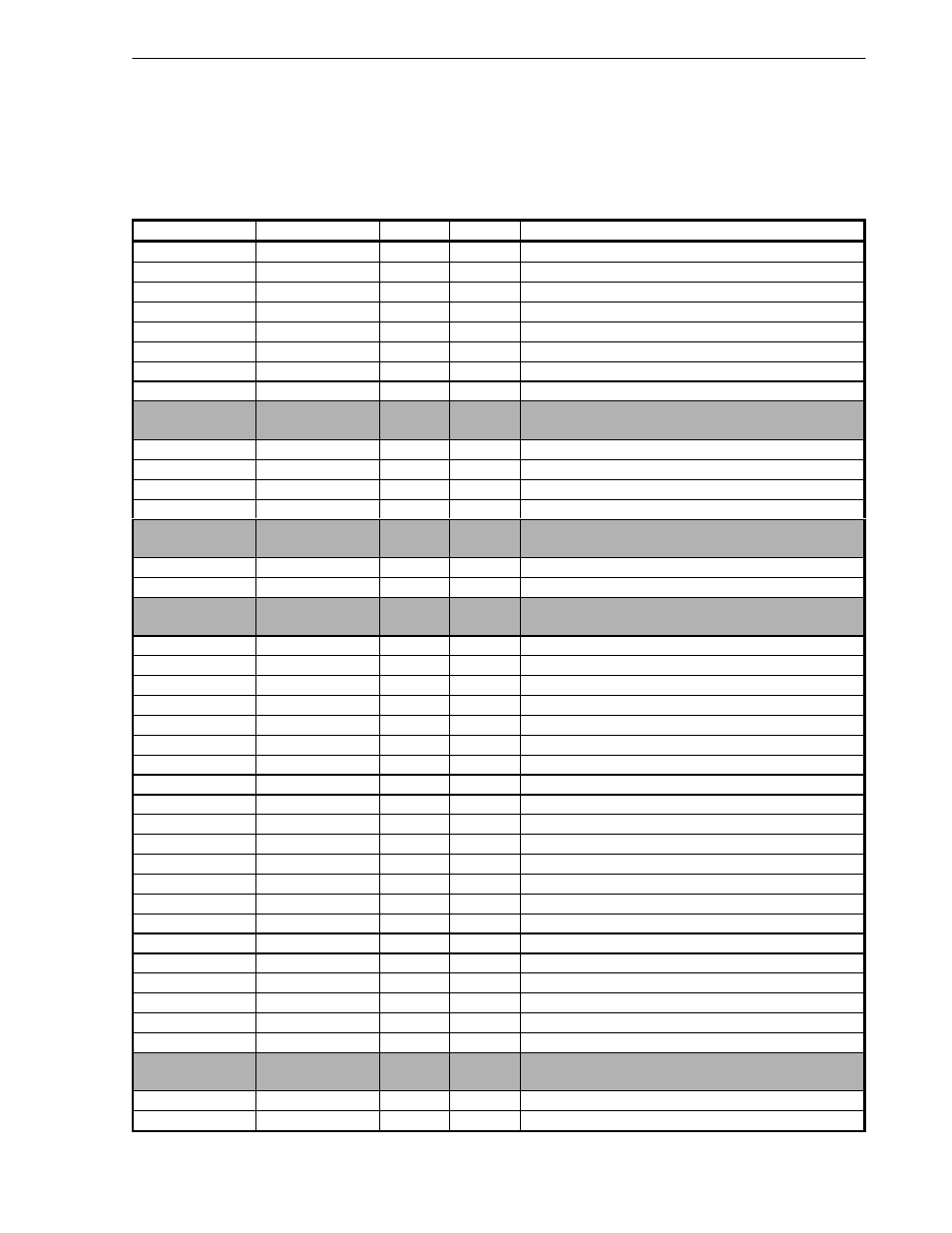

3.2 Registers

3.2.1 Register map

Following Table summarizes the controller’s register set. The base address for the set is 1000_0000H in the

physical address space.

Offset Address

Register Name

R/W

Access

Description

1000_0000H

S_GMR

R/W

W/H/B

General Mode Register

1000_0004H

S_GSR

R

W/H/B

General Status Register

1000_0008H

S_ISR

RC

W/H/B

Interrupt Status Register

1000_000CH

S_IMR

R/W

W/H/B

Interrupt Mask Register

1000_0010H

S_NSR

RC

W/H/B

NMI Status Register

1000_0014H

S_NER

R/W

W/H/B

NMI Enable Register

1000_0018H

S_VER

R

W/H/B

Version Register

1000_001CH

S_IOR

R/W

W/H/B

IO Port Register

1000_0020H:

1000_002CH

N/A

-

-

Reserved for future use

1000_0030H

S_WRCR

W

W/H/B

Warm Reset Control Register

1000_0034H

S_WRSR

R

W/H/B

Warm Reset Status Register

1000_0038H

S_PWCR

R/W

W/H/B

Power Control Register

1000_003CH

S_PWSR

R

W/H/B

Power Control Status Register

1000_0040H:

1000_0048H

N/A

-

-

Reserved for future use

1000_004CH

ITCNTR

R/W

W/H/B

IBUS Timeout Timer Control Register

1000_0050H

ITSETR

R/W

W/H/B

IBUS Timeout Timer Set Register

1000_0054H:

1000_007CH

N/A

-

-

Reserved for future use

1000_0080H

UARTRBR

R

W/H/B

UART, Receiver Buffer Register [DLAB=0,READ]

1000_0080H

UARTTHR

W

W/H/B

UART, Transmitter Holding Register [DLAB=0,WRITE]

1000_0080H

UARTDLL

R/W

W/H/B

UART, Divisor Latch LSB Register [DLAB=1]

1000_0084H

UARTIER

R/W

W/H/B

UART, Interrupt Enable Register [DLAB=0]

1000_0084H

UARTDLM

R/W

W/H/B

UART, Divisor Latch MSB Register [DLAB=1]

1000_0088H

UARTIIR

R

W/H/B

UART, Interrupt ID Register [READ]

1000_0088H

UARTFCR

W

W/H/B

UART, FIFO control Register [WRITE]

1000_008CH

UARTLCR

R/W

W/H/B

UART, Line control Register

1000_0090H

UARTMCR

R/W

W/H/B

UART, Modem Control Register

1000_0094H

UARTLSR

R/W

W/H/B

UART, Line status Register

1000_0098H

UARTMSR

R/W

W/H/B

UART, Modem Status Register

1000_009CH

UARTSCR

R/W

W/H/B

UART, Scratch Register

1000_00A0H

DSUCNTR

R/W

W/H/B

DSU Control Register

1000_00A4H

DSUSETR

R/W

W/H/B

DSU Dead Time Set Register

1000_00A8H

DSUCLRR

W

W/H/B

DSU Clear Register

1000_00ACH

DSUTIMR

R

W/H/B

DSU Elapsed Time Register

1000_00B0H

TMMR

R/W

W/H/B

Timer Mode Register

1000_00B4H

TM0CSR

R/W

W/H/B

Timer CH0 Count Set Register

1000_00B8H

TM1CSR

R/W

W/H/B

Timer CH1 Count Set Register

1000_00BCH

TM0CCR

R

W/H/B

Timer CH0 Current Count Register

1000_00C0H

TM1CCR

R

W/H/B

Timer CH1 Current Count Register

1000_00C4H:

1000_00CCH

N/A

-

-

Reserved for future use

1000_00D0H

ECCR

W

W/H/B

EEPROM Command Control Register

1000_00D4H

ERDR

R

W/H/B

EEPROM Read Data Register