NEC Network Controller uPD98502 User Manual

Page 436

APPENDIX A MIPS III INSTRUCTION SET DETAILS

436

Preliminary User’s Manual S15543EJ1V0UM

ADD

Add

ADD

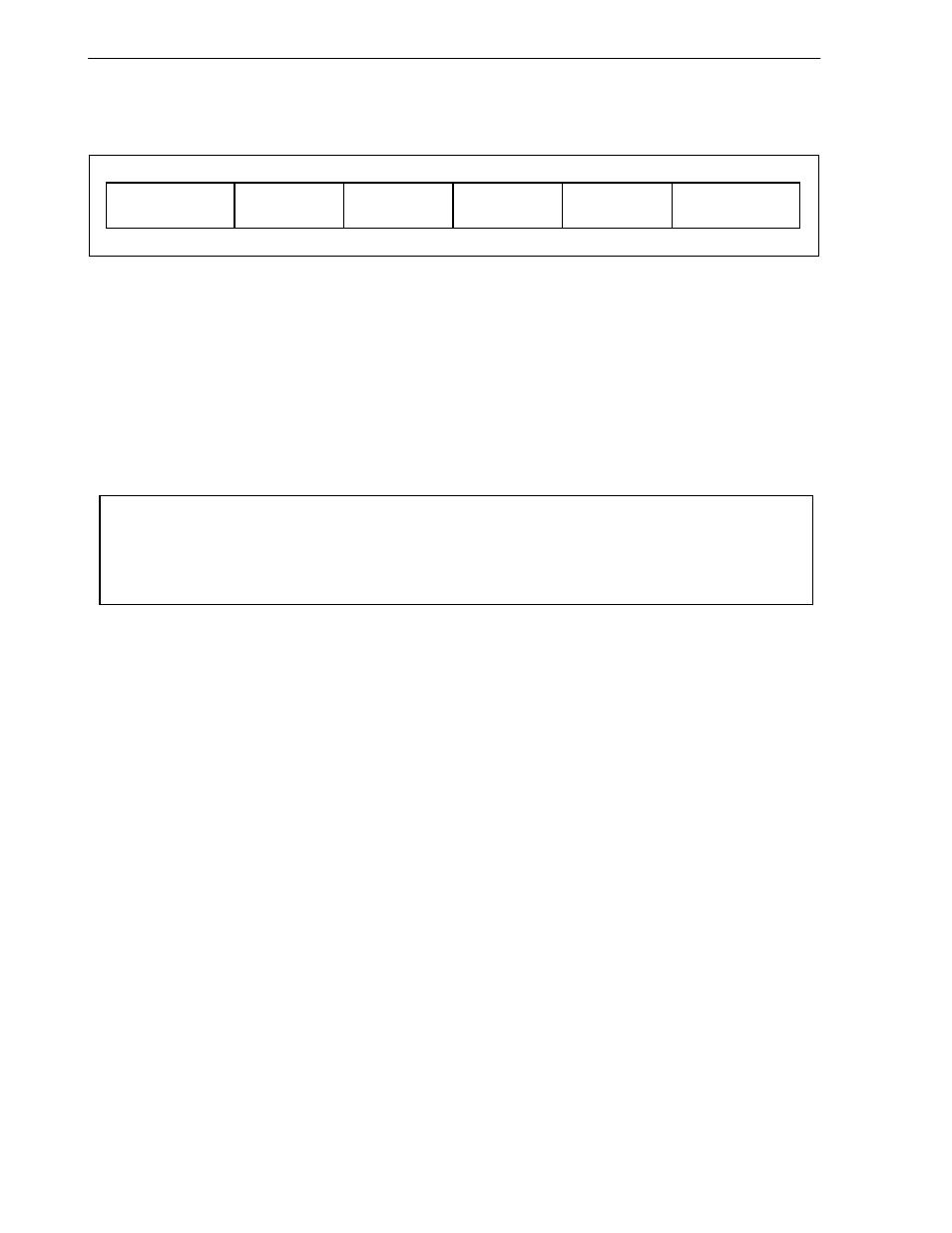

rs

SPECIAL

0 0 0 0 0 0

rt

rd

0

0 0 0 0 0

ADD

1 0 0 0 0 0

31

26 25

21 20

16 15

11 10

6 5

0

6

5

5

5

5

6

Format:

ADD rd, rs, rt

Description:

The contents of general register

rs and the contents of general register rt are added to form the result. The result

is placed into general register

rd. In 64-bit mode, the operands must be valid sign-extended, 32-bit values.

An overflow exception occurs if the carries out of bits 30 and 31 differ (2's complement overflow). The destination

register

rd is not modified when an integer overflow exception occurs.

Operation:

32

T:

GPR [rd]

← GPR [rs] + GPR [rt]

64

T:

temp

← GPR [rs] + GPR [rt]

GPR [rd]

← (temp

31

)

32

|| temp

31...0

Exceptions:

Integer overflow exception