Dsllv, Doubleword shift left logical variable – NEC Network Controller uPD98502 User Manual

Page 485

APPENDIX A MIPS III INSTRUCTION SET DETAILS

Preliminary User’s Manual S15543EJ1V0UM

485

DSLLV

Doubleword Shift Left Logical Variable

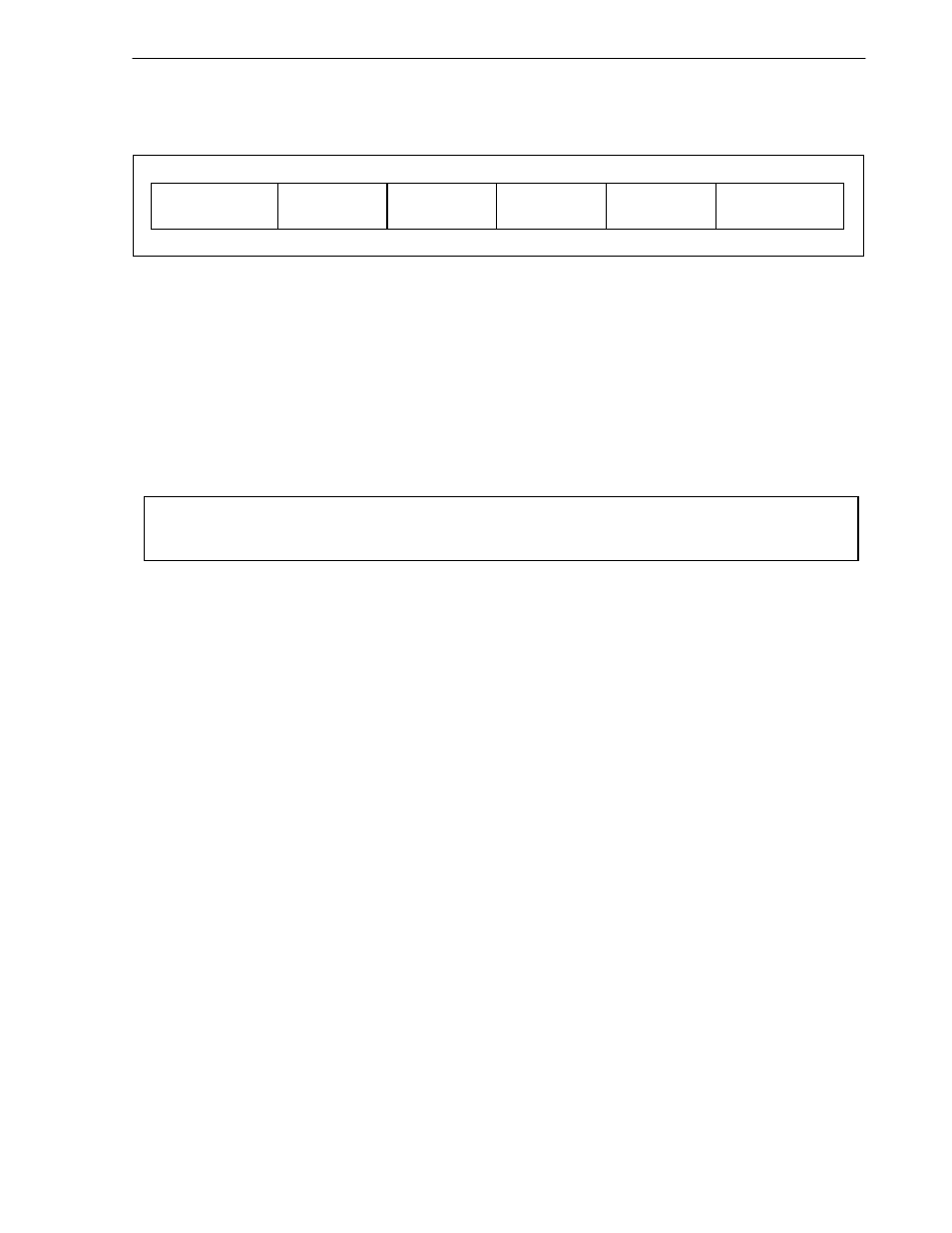

DSLLV

rs

SPECIAL

0 0 0 0 0 0

rt

rd

0

0 0 0 0 0

DSLLV

0 1 0 1 0 0

31

26 25

21 20

16 15

11 10

6 5

0

6

5

5

5

5

6

Format:

DSLLV rd, rt, rs

Description:

The contents of general register

rt are shifted left by the number of bits specified by the low-order six bits contained

in general register

rs, inserting zeros into the low-order bits. The result is placed in register rd.

This operation is defined in 64-bit mode or in 32-bit kernel mode. Execution of this instruction in 32-bit user or

supervisor mode causes a reserved instruction exception.

Operation:

64

T:

s

← GPR [rs]

5..0

GPR [rd]

← GPR [rt]

(63 - s)..0

|| 0

s

Exceptions:

Reserved instruction exception (32-bit user mode/supervisor mode)