4 frame transmission – NEC Network Controller uPD98502 User Manual

Page 302

CHAPTER 5 ETHERNET CONTROLLER

302

Preliminary User’s Manual S15543EJ1V0UM

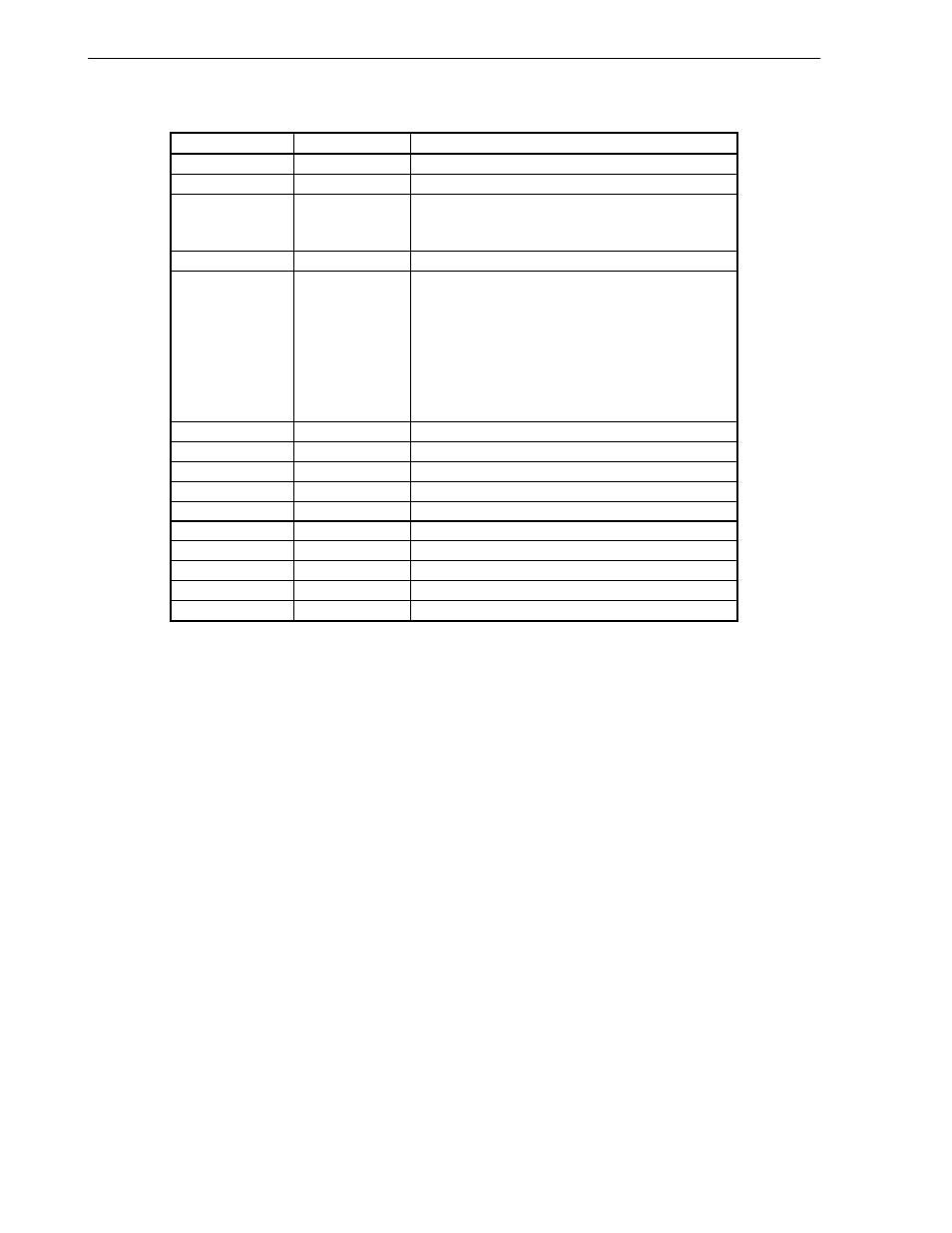

Table 5-7. Attribute for Receive Descriptor

Attribute & Size

Bit Name

Status

31

L

Last Descriptor

30

D/L

Data Buffer / Link Pointer

29

OWN

Owner bit 1:Ethernet Controller 0: V

R

4120A

Ethernet Controller sets this bit after it began to transfer

data into each descriptor.

28

DBWE

Data Buffer Write Error

27:25

FTYP

Frame Type[2:0]:

000 Broadcast Frame

001 Multicast Frame

010 Unicast Frame

011 VLAN Frame

100 PAUSE control frame

101 Control Frame (except pause)

11x Reserved for future use

24

OVRN

Overrun Error

23

0

Reserved for future use.

22

0

Reserved for future use.

21

RCV

Detects RXER

20

FC

False Carrier

19

CRCE

CRC Error

18

FAE

Frame Alignment Error

17

RFLE

Receive Frame Length Error

16

RXOK

Receive OK

15:0

SIZE

Receive Byte Count

Remark

RUNT packet:

less than 64 bytes packet with a good FCS

FRAGMENT packet: less than 64 bytes packet with either a bad FCS or a bad FCS with an

alignment error

Dribble Error:

When a dribble error is occurred, both of RXOK and FAD will be set.

5.3.4 Frame transmission

The transmitter is designed to work with almost no intervention from the V

R

4120A. Once the V

R

4120A enables the

transmitter by setting the Transmit Descriptor Pointer Register (En_TXDPR) and the Transmit Enable (TXE), Ethernet

Controller fetches the first Transmit Data Buffer from Buffer Descriptor.

When the drain threshold level of the transmit FIFO was over, the MAC Controller Block transmit logic will start

transmitting the preamble sequence, the start frame delimiter, and then the frame information. However, the controller

defers the transmission if the line is busy (carrier sense is active). Before transmitting, the controller has to wait for

carrier sense to become inactive. Once carrier sense is inactive, the controller determines if carrier sense stays

inactive for IPGR1 bit time in En_IPGR register. If so, then the transmission begins after waiting an additional IPGR2 –

IPGR1 bit times (i.e., IPG is generally 96 bit times).

If a collision occurs during the transmit frame, Ethernet Controller follows the specified back-off procedures and

attempts to re-transmit the frame until the retry limit threshold is reached (RETRY in En_CLRT register). Ethernet

Controller holds the first 64 bytes of the transmit frame in the transmit FIFO, so that Ethernet Controller does not have

to be retrieved from system memory in case of a collision. This improves bus utilization and latency.

When Ethernet Controller reads the Transmit Buffer Descriptor, and it shows the end of data buffer “L bit is set to a

‘1’, Ethernet Controller adds the FCS after the end of data if CRCEN in En_MACC1 register is enable.