1 work ram and register space, 2 shared memory, 3 interruption – NEC Network Controller uPD98502 User Manual

Page 237

CHAPTER 4 ATM CELL PROCESSOR

Preliminary User’s Manual S15543EJ1V0UM

237

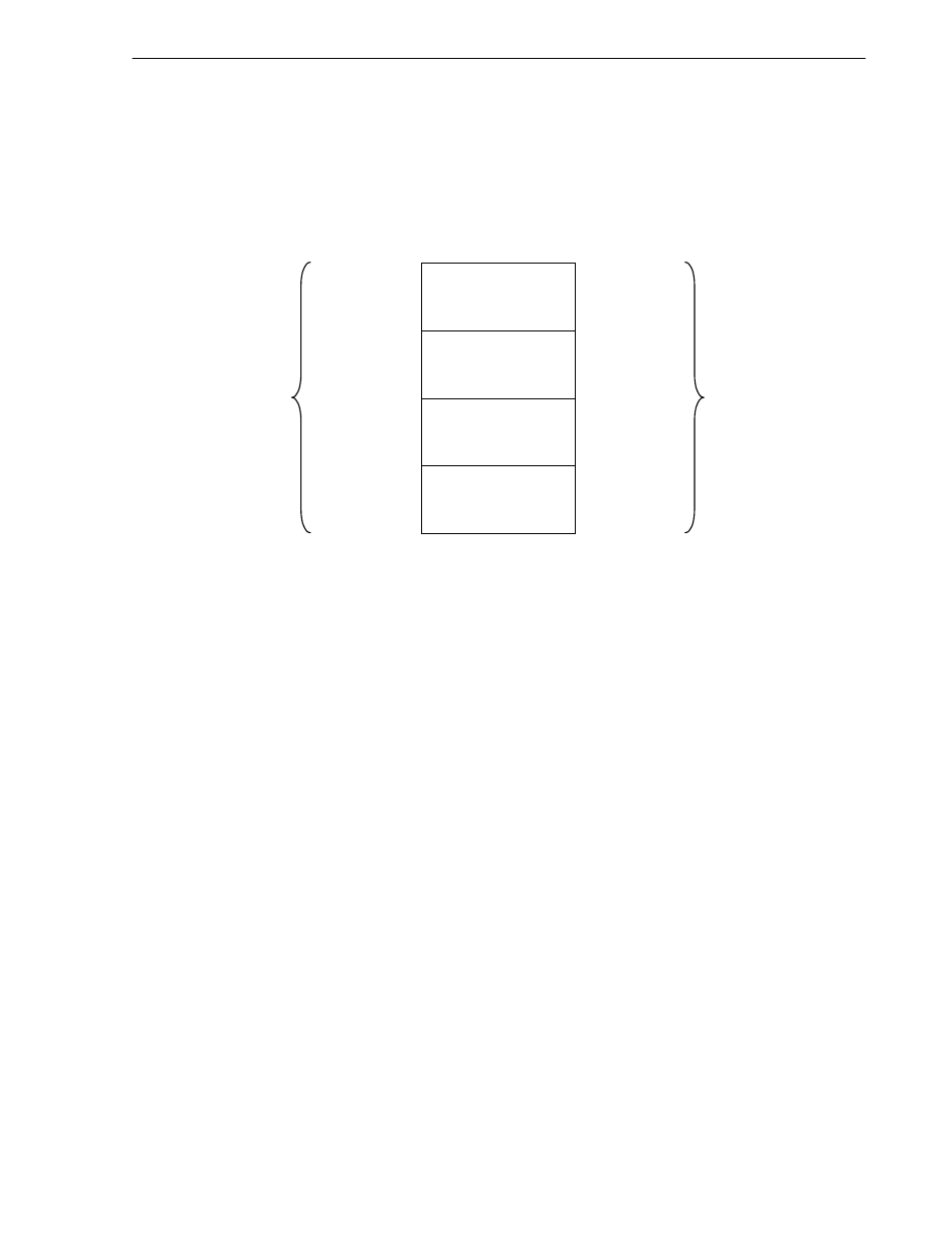

4.2.1 Work RAM and register space

Work RAM and Register Space are shown in Figure 4-7. The capacity of Work RAM is 16 KB max. In order to

access Work RAM, the user has to use “Indirect Access Command”. In register space, A_GMR (general mode

register), A_GSR (general status register), A_CMR (command register), A_CER (command extension register) and

other registers will be mapped. In PHY space, PHY devices can be accessed through UTOPIA management I/F.

Figure 4-7. Work RAM and Register Space

xx80_FFFFH

1001_FFFFH

xx80_F000H

ATM Cell Processor

Registers

1001_F000H

xx80_E000H

Reserved for

PHY Devices

1001_E000H

xx80_3FFFH

1001_3FFFH

xx80_0000H

Work RAM

(16 KB)

1001_0000H

Internal memory space and peripheral space are exclusively used by RISC Core and cannot be seen by other

blocks. Internal memory space will be used as stack and global variable space. In peripheral space, an interrupt

controller and some other special blocks will be mapped. Scheduling table, VC lookup table and Cell Timer will be

mapped in peripheral space as well.

4.2.2 Shared memory

ATM Cell Processor can access 4 MB or less of the memory space that is used as cell buffer and packet buffer. It

is also used for instruction memory. This memory will be implemented off the chip. RISC Core in the ATM Cell

Processor can access this memory through System Controller. From the RISC Core’s point of view the base address

to access the memory should be written to A_IBBAR (IBUS data Base Address Register). A_IBBAR will be set during

initializing period.

4.3 Interruption

When any bit in A_GSR (General Status Register) is NOT set to a ‘1’, that is, an interruption will be issued to

V

R

4120A. The status of interruption is obtained by reading in A_GSR. When V

R

4120A reads A_GSR, the bits which

are set and are NOT masked using A_IMR will be reset. The interruption can be masked by resetting bits of

corresponding incidents in A_IMR (Interrupt Mask Register).

Interruptions from PHY devices are forwarded to V

R

4120A by PI bit of A_GSR automatically.

From

RISC Core’s

point of view

From

V

R

4120A’s

point of view