1 i2c receive buffer descriptor (rxbd), I2c rxbd status and control bits -13, C receive buffer descriptor (rxbd) – Motorola MPC8260 User Manual

Page 955: C controller is enabled. table 34-9 describes i, C rxbd status and control bits

MOTOROLA

Chapter 34. I2C Controller

34-13

Part IV. Communications Processor Module

34.7.1.1 I

2

C Receive Buffer Descriptor (RxBD)

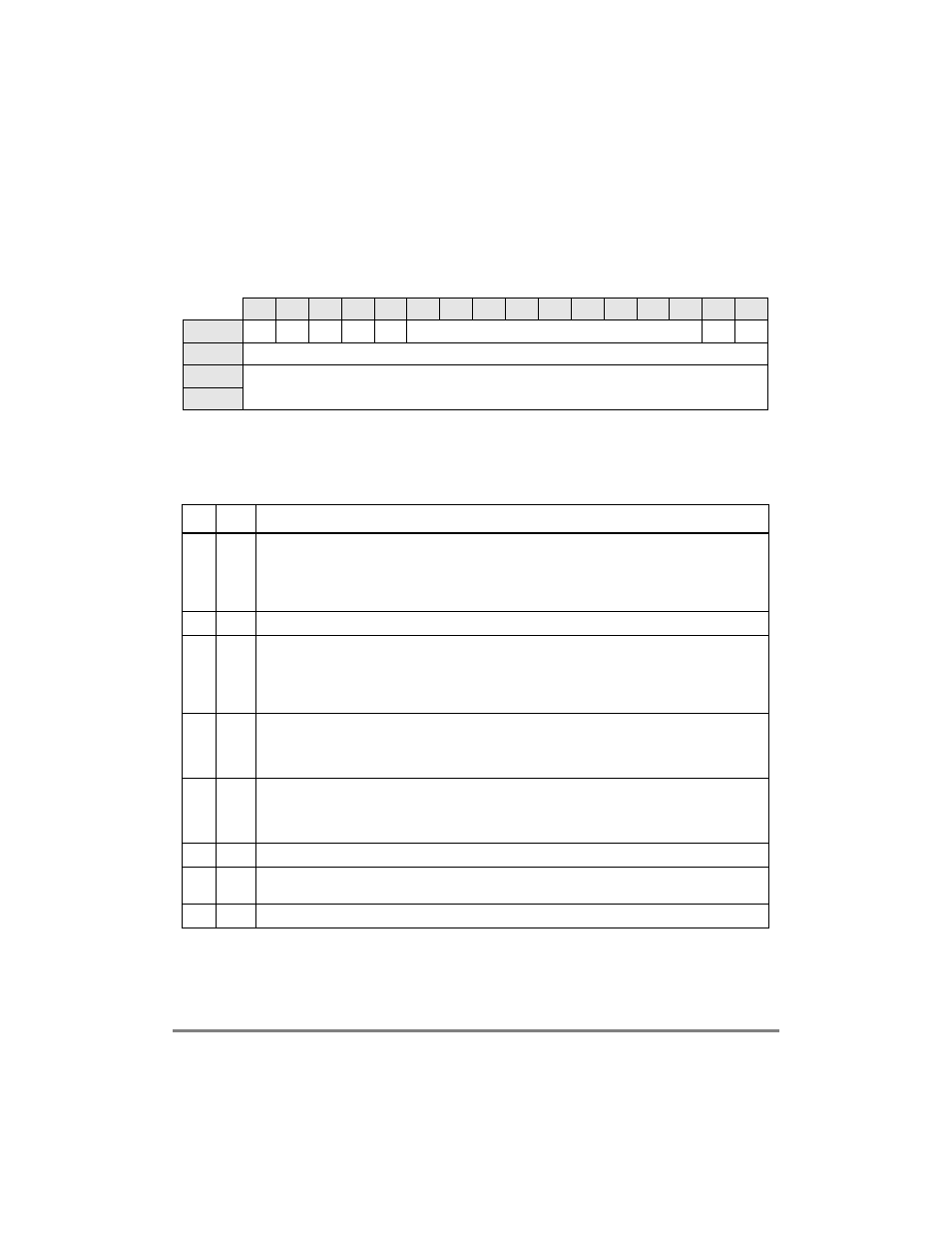

Using RxBDs, the CP reports on each buffer received, closes the current buffer, generates

a maskable interrupt, and starts receiving data in the next buffer when the current one is full.

It closes the buffer when a stop or start condition is found on the I

2

C bus or when an overrun

error occurs. The core should write RxBD bits before the I

2

C controller is enabled.

2

C RxBD status and control bits.

0

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

Offset + 0

E

Ñ

W

I

L

Ñ

OV

Ñ

Offset + 2

Data Length

Offset + 4

RX Buffer Pointer

Offset + 6

Figure 34-13. I

2

C RxBD

Table 34-9. I

2

C RxBD Status and Control Bits

Bits

Name

Description

0

E

Empty.

0 The buffer is full or stopped receiving because of an error. The core can examine or write to any

Þelds of this RxBD, but the CP does not use this BD while E = 0.

1 The buffer is empty or reception is in progress. The CP owns this RxBD and its buffer. Once E is set,

the core should not write any Þelds of this RxBD.

1

Ñ

Reserved and should be cleared.

2

W

Wrap (last BD in table).

0 Not the last BD in the RxBD table.

1 Last BD in the RxBD table. After this buffer is used, the CP receives incoming data using the BD

pointed to by RBASE (top of the table). The number of BDs in this table is determined only by the W

bit and overall space constraints of the dual-port RAM.

3

I

Interrupt.

0 No interrupt is generated after this buffer is full.

1 The I2CER[RXB] is set when the CP Þlls this buffer, indicating that the core needs to process the

buffer. The RXB bit can cause an interrupt if it is enabled.

4

L

Last. The I

2

C controller sets L.

0 This buffer does not contain the last character of the message.

1 This buffer holds the last character of the message. The I

2

C controller sets L after all received data is

placed into the associated buffer, or because of a stop or start condition or an overrun.

5Р13 С

Reserved and should be cleared.

14

OV

Overrun. Set when a receiver overrun occurs during reception. The I

2

C controller updates this bit after

the received data is placed into the associated buffer.

15

Ñ

Reserved and should be cleared.