8 system protection control register (sypcr), System protection control register (sypcr) -35, System protection control register (sypccr) -35 – Motorola MPC8260 User Manual

Page 173: Sypcr field descriptions -35

4-35

MPC8260 PowerQUICC II UserÕs Manual

MOTOROLA

Part II. ConÞguration and Reset

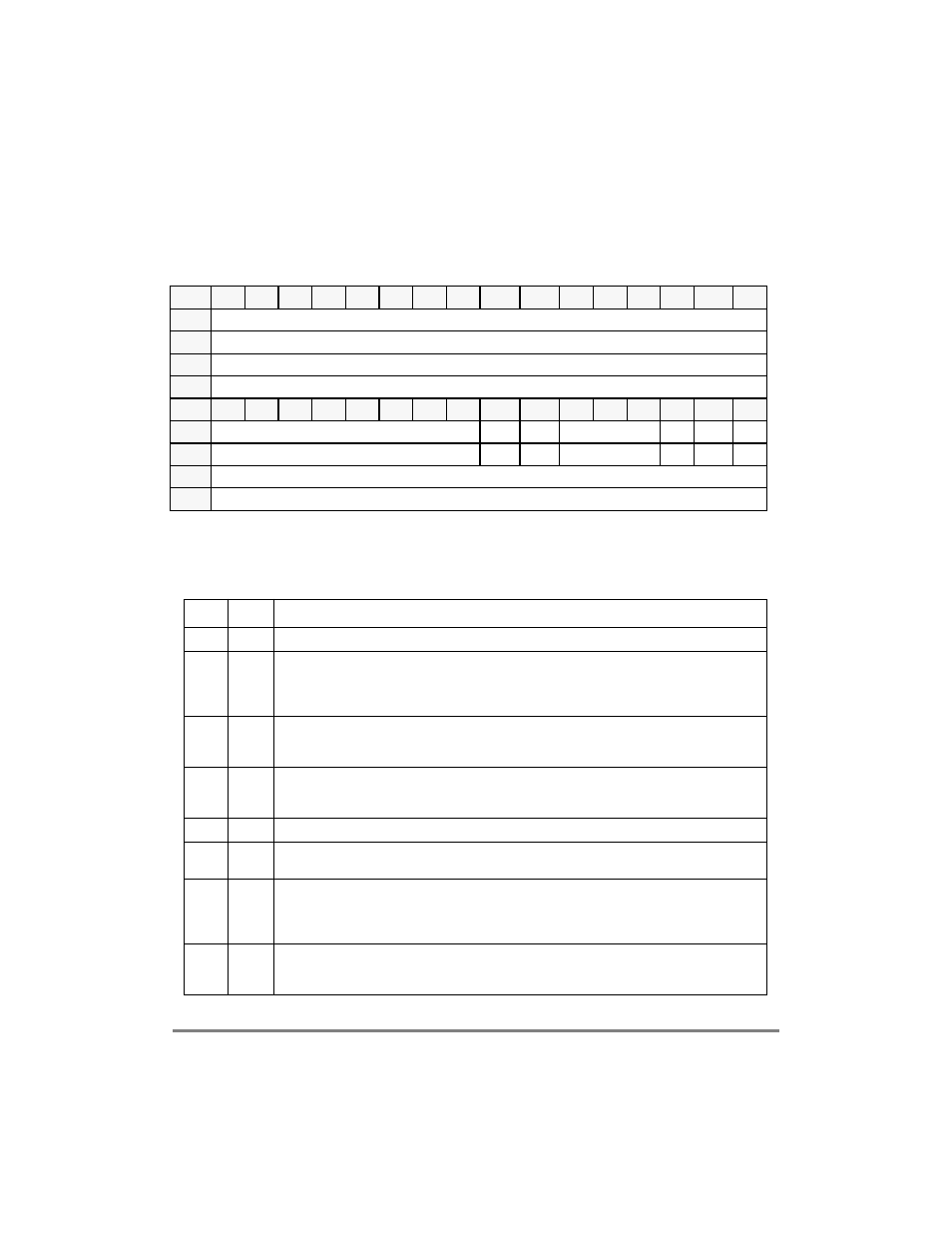

4.3.2.8 System Protection Control Register (SYPCR)

The system protection control register, shown in Figure 4-30, controls the system monitors,

software watchdog period, and bus monitor timing. SYPCR can be read at any time but can

be written only once after system reset.

Table 4-14 describes SYPCR Þelds.

Bits

0

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

Field

SWTC

Reset

1111_1111_1111_1111

R/W

R/W

Addr

Bits

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

Field

BMT

PBME LBME

Ñ

SWE SWRI SWP

Reset

1111_1111

0

0

00_0

1

1

1

R/W

R/W

Addr

0x10006

Figure 4-30. System Protection Control Register (SYPCCR)

Table 4-14. SYPCR Field Descriptions

Bits

Name

Description

0Ð15

SWTC Software watchdog timer count. Contains the count value for the software watchdog timer.

16Ð23

BMT

Bus monitor timing. DeÞnes the time-out period for the bus monitor, the granularity of this Þeld is 8

bus clocks. (BMT = 0xFF is translated to 0x7f8 clock cycles). BMT is used both in the 60x and local

bus monitors.

Note that the value 0 in invalid; an error is generated for each bus transaction.

24

PBME

60x bus monitor enable.

0 60x bus monitor is disabled.

1 The 60x bus monitor is enabled.

25

LBME

Local bus monitor enable.

0 Local bus monitor is disabled.

1 The local bus monitor is enabled.

26Р29

С

Reserved, should be cleared.

29

SWE

Software watchdog enable. Enables the operation of the software watchdog timer. It should be

cleared by software after a system reset to disable the software watchdog timer.

30

SWRI

Software watchdog reset/interrupt select.

0 Software watchdog timer and bus monitor time-out causes a machine check interrupt to the core.

1 Software watchdog timer and bus monitor time-out causes a soft reset (this is the default value

after soft reset).

31

SWP

Software watchdog prescale. Controls the divide-by-2,048 software watchdog timer prescaler.

0 The software watchdog timer is not prescaled.

1 The software watchdog timer clock is prescaled.