7 processor state signals, Processor state signals -32 – Motorola MPC8260 User Manual

Page 264

8-32

MPC8260 PowerQUICC II UserÕs Manual

MOTOROLA

Part III. The Hardware Interface

When the MPC8260 processor is not the address bus master, GBL is an input. The

MPC8260 processor snoops a transaction if TS and GBL are asserted together in the same

bus clock cycle (a qualiÞed snooping condition). No snoop update to the MPC8260

processor cache occurs if the transaction is not marked global. This includes invalidation

cycles.

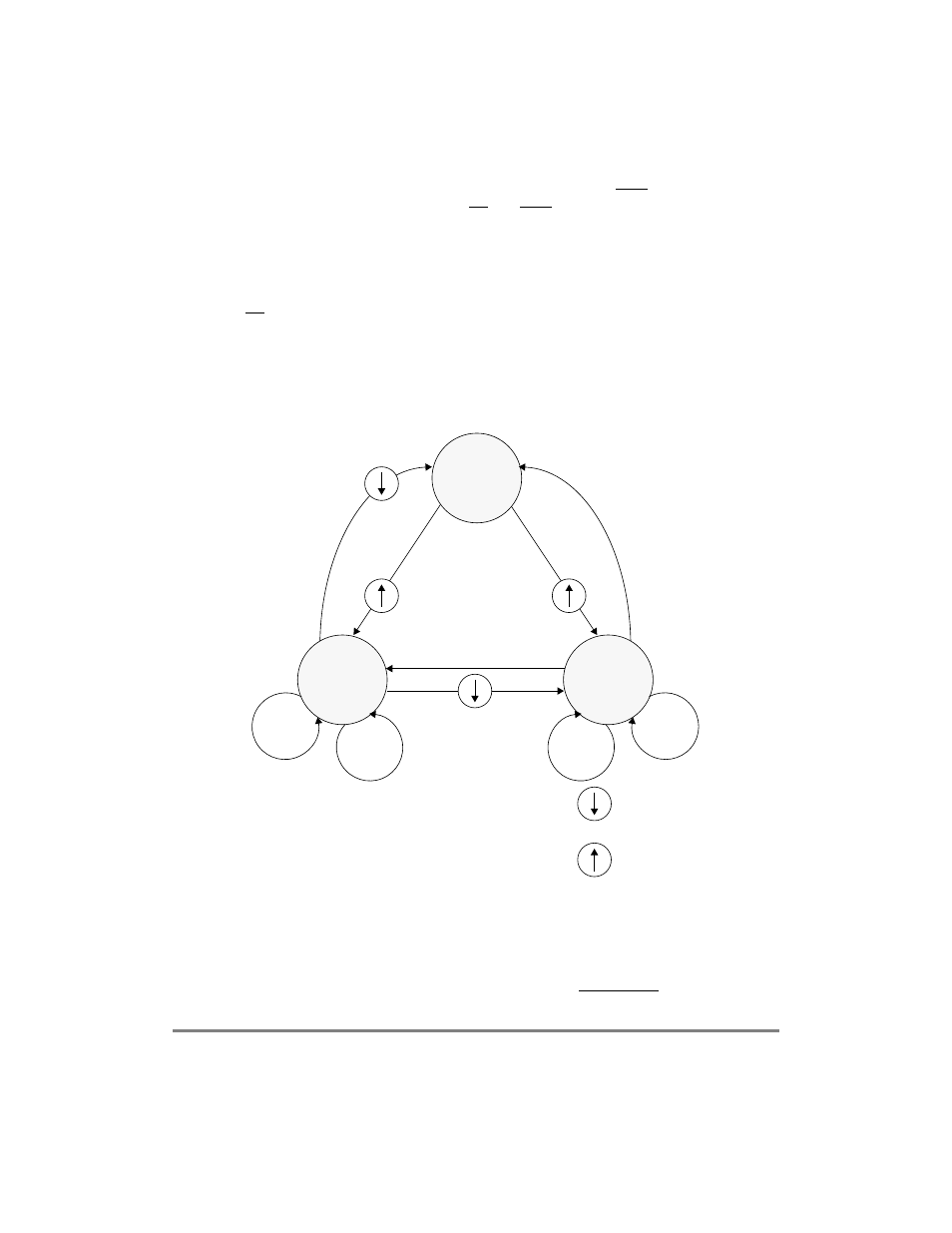

When the MPC8260 processor detects a qualiÞed snoop condition, the address associated

with the TS is compared against the data cache tags. Snooping completes if no hit is

detected. However, if the address hits in the cache, the MPC8260 processor reacts

according to the MEI protocol shown in Figure 8-12. This Þgure assumes that

WIM = 0b001 (memory space is marked for write-back, caching-allowed, and coherency-

enforced modes).

Figure 8-12. MEI Cache Coherency ProtocolÑState Diagram (WIM = 001)

8.7 Processor State Signals

This section describes the MPC8260Õs support for atomic update and memory through the

use of the lwarx/stwcx. instruction pair. It also describes the TLBISYNC input.

Invalid

Modified

WH

SH

SH/CRW

WM

WH

RH

SH = Snoop hit

RH = Read hit

WH = Write hit

WM = Write miss

RM = Read miss

SH/CRW = Snoop hit, cacheable read/write

SH/CIR = Snoop hit, cache-inhibited read

= Snoop push

= Cache line fill

Exclusive

SH/CRW

RM

SH/CIR

RH