User-programmable machine block diagram -63 – Motorola MPC8260 User Manual

Page 339

MOTOROLA

Chapter 10. Memory Controller

10-63

Part III. The Hardware Interface

Additional control is available in 60x-compatible mode (60x bus only)ÑALEÑExternal

address latch enable (not a UPM-controlled signal).

Note that in this section, when a signal is named, the reference is to the 60x or local bus

signal, according to the bank being accessed.

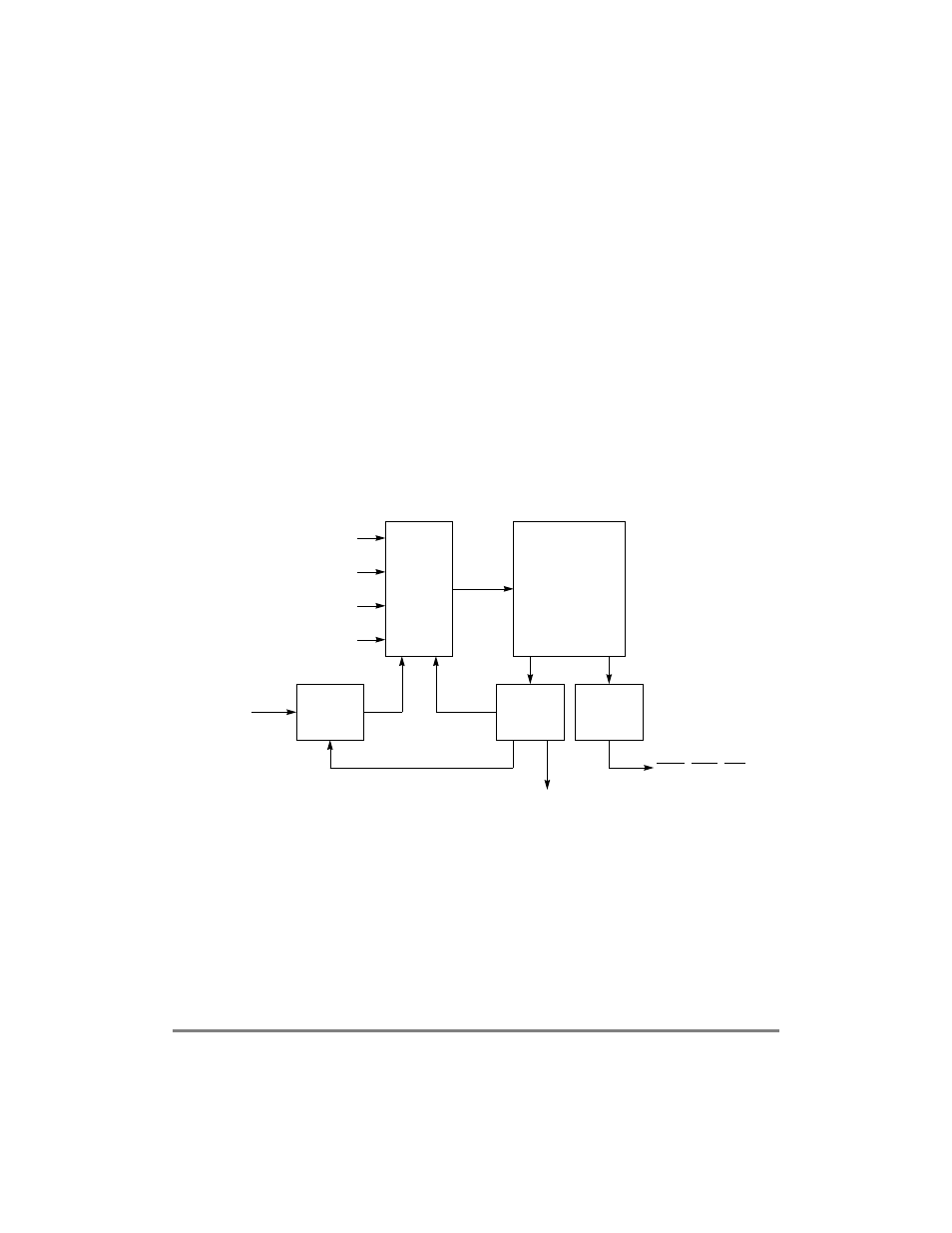

The three user-programmable machines (UPMs) are ßexible interfaces that connect to a

wide range of memory devices. At the heart of each UPM is an internal-memory RAM

array that speciÞes the logical value driven on the external memory controller pins for a

given clock cycle. Each word in the RAM array provides bits that allow a memory access

to be controlled with a resolution of up to one quarter of the external bus clock period on

the byte-select and chip-select lines. Figure 10-55 shows the basic operation of each UPM.

The following events initiate a UPM cycle:

¥

Any internal or external device requests an external memory access to an address

space mapped to a chip-select serviced by the UPM

¥

A UPM refresh timer expires and requests a transaction, such as a DRAM refresh

¥

A transfer error or reset generates an exception request

Figure 10-55. User-Programmable Machine Block Diagram

The RAM array contains 64 32-bit RAM words. The signal timing generator loads the

RAM word from the RAM array to drive the general-purpose lines, byte-selects, and

chip-selects. If the UPM reads a RAM word with WAEN set, the external UPWAIT signal

is sampled and synchronized by the memory controller and the current request is frozen.

When a new access to external memory is requested by any device on the 60x or local bus,

the addresses of the transfer are compared to each one of the valid banks deÞned in the

memory controller. When an address match is found in one of the memory banks, BRx[MS]

selects the UPM to handle this memory access. MxMR[BS] assigns the UPM to the 60x or

the local bus.

RUN

command

UPM refresh

timer request

Array

Index

Generator

Internal/external

memory access request

Exception request

Index

Signals

Timing

Generator

Internal

Signals

Latch

Wait

Request

Logic

RAM Array

UPWAIT

WAEN Bit

Internal Controls

GPLx, BS_x, CSx

Increment

Index

(LAST = 0)

Hold

(issued in software)